PulseGenerator : IHM face avant

Vous pouvez rédiger vos propositions sur cette page, ou-bien nous les envoyer sur la liste de diffusion du projet ;-)

Suggestion d'IHM pour la face avant

Suggestion d'IHM pour la face avant

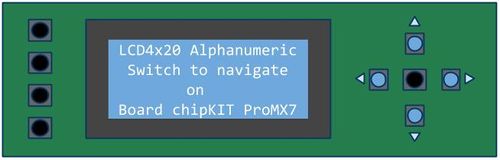

Présentation "IHM LCD 4x20", conçu lors de la formation PIC32 ;-)

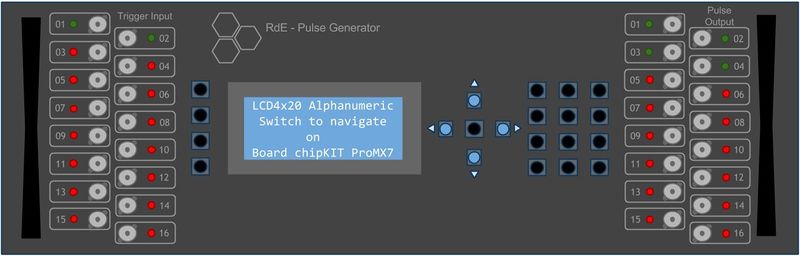

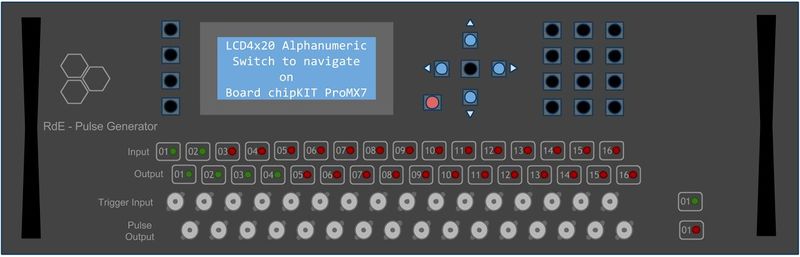

Proposition pour l'intégration dans un boitier rackable 19" au format 4U (les dessins ne sont pas à l’échelle) :

- PG Face Avant Version A.0 avec BNC à gauche pour les entrées et à droite pour les sorties

- PG Face Avant Version A.1 idem mais avec les LEDs et sérigraphie en plus

- PG Face Avant Version A.2 en partant de la version A.1, cette nouvelle version présente une face avant avec 8 entrées et 8 sorties comprenant en entrée un connecteur BNC + un connecteur pour Fibre Optique + un bouton poussoir + une LED bicolore, et pour la sortie on aura la LED bicolore + une LED Optique + une BNC.

- PG Face Avant Version A.3 idem à la version A.2, avec 8 entrées et 16 sorties.

- PG Face Avant Version A.4 idem à la version A.3, mais en optimisant l'interface de navigation, cela permet d'avoir uniquement une matrice de 4 par 4 au niveau des boutons poussoir, voir "l'usinage des boutons poussoirs"

- PG Face Avant Version A.5 idem à la version A.4, ré-organisation du pad et du clavier, remplacement de l'écran LCD 4x20 par un écran LCD "uLCD-43-PT de 4D Systems" (version en cours de validation)

- PG Face Avant Version B.0 avec BNC en partie basse du boitier pour une répartition moins serré de l'IHM (permet peut-être d'être moins gêné par les BNC et d'avoir plus d'espace pour les branchements)

Connexion de la carte chipKIT™ Pro MX7 (CEREBOT™ MX7cK)

voir le tableau de synthèse "Ressources PIC32_CHIPKIT_PRO_MX7_BOARD pour PG"

Les tableaux suivants donne les correspondances entre les éléments de la face avant et les broches des connecteurs Pmod:

|

Proposition pour le raccordement en maillage de 12 boutons poussoir :

|

|

Proposition pour le raccordement en maillage de 16 boutons poussoir (voir PmodKYPD) :

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Raccordement de l'afficheurs LCD alphanumérique 4x20 :

|

|

Liaison SPI maître vers la carte CPLD :

|

Fichier:Nuvola apps kate.png Recensement des besoins de chacun pour la conception du proto

Nous pourrions utiliser un logiciel libre et Open source pour la réalisation des PCB. KiCad semble un bon candidat...

Hardware

Hardware

voir la "Nomenclature pour commande projet Pulse Generator"

- carte Nexys™4 Artix-7 FPGA Board

- 8 entrées Trigger avec 3 entrées raccordées sur une carte logique "OU" dont une BNC, une Fibre Optique et un bouton poussoir

- de 16 à 32 voies en sortie avec des délais différents

- entrées et sorties compatible TTL, voir Logic Level Converter Bi-Directional

- interface électronique pour Trigger permettant de convertir un signal TTL (0-5 V) vers l'entrée 3V3 du FPGA/CPLD

- 2 BNC 50 Ohms par voie (Trigger + Pulse), montées sur panneau avant pour en facilité l'accès

- 1 LED (bicolore) pourrait-être ajouté à coté de chaque BNC pour visualiser la configuration des Trigger en association avec les voies de sortie, ainsi que le déclenchement de ces dernières

- entrée "Alimentation Signal de sortie" sur face arrière, pour fixer depuis des collecteurs ouverts le niveau de tension des sorties des signaux Pulse

- faire une carte fond de panier ou carte mère pour pouvoir raccorder plusieurs cartes CPLD avec la face arrière

- souhait de ne pas avoir de jitter sur la durée des pulses

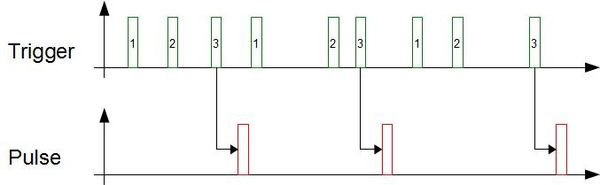

- comptage du nombre de trigger avant la génération du pulse, exemple:

- avoir les boutons suivant:

- pavé de navigation 5 voies → RS Components: 126-846

- boutons pour séquenceur: Pause / Stop / Reset → ? proposer un modèle de face avant, si validé...

- RTCC pour horodatage des événements (TDGL013 - Digilent PmodRTCC Peripheral Module)

- firmware USB Host sur la carte PIC32 → Sauvegarde et restauration de configuration utilisateur + fichier LOG sur clef USB (fiche USB type A en face avant)

Intégration mécanique

Intégration mécanique

- coffret montage sur rack 19" 4U, Code commande RS: 665-7722

- ou 3U, Code commande RS: 665-7725

- + rack 19" 1U, qui pourrait être rajouter pour réaliser 2x 16 voies BNC (16x Trigger + 16x Pulse OUT) en face avant comme autant de modules optionnels que de voies désirées

- baie au format PCI et non PXI ?

- voir aussi easy-phi: High-speed pulse generator

- un boitier pour paillasse, référence ?

Fonctionnement depuis l'IHM de la face avant

Fonctionnement depuis l'IHM de la face avant

- un écran d’accueil (Splash screen) affiché pendent 5 sec, voici quelques propositions, pensez aux présentations pour les prochaines rencontres dans les réseaux :

"""""""""""""""""""""" ".:: AAP RdE 2013 ::." "Projet Collaboratif " " _ Pulse Generator " "_/ Firmware v1.00 " """"""""""""""""""""""

-------------------- ".:: AAP RdE 2013 ::." " Projet Collaboratif" " _ Pulse Generator " "_/ \_ Firmware v1.00" --------------------

- Gestion des menus par une variable d'environnement "Current_Menu" pour rendre le fonctionnement du PIC fluide. Description des valeurs :

- 00 = MAIN_MENU : menu principale, navigation mais pas de sélection en cours

- 10 = ... : menu 1

- 20 = ... : menu 2

- 30 = ... : menu 3

- 31 = ... : sous menu 3-1

- 32 = ... : sous menu 3-2

- 33 = ... : sous menu 3-3

- 40 = ... : menu 4

- 41 = ... : sous menu 4-1

- 42 = ... : sous menu 4-2

- et un grand SWITCH CASE pour gérer tout ça dans la boucle while(1) du main

- On peut imaginer d'avoir une navigation dans les menus qui soit intuitives (plutôt qu'un grand nombre de bouton), par exemple pour le niveau 1 "Pulse Setting", puis ('→' marquant la transition lors de la sélection par l'utilisateur) on choisi la voie à configurer, avant d'accéder en niveau 2 pour le paramétrage des timing...

NIV1.L1 "--Menu: Principale--" NIV1.L2 "> Pulse Setting [--]" → ">Pulse Setting [32]<" → puis aller vers niveau 2 pour le paramétrage de la voie sélectionnée NIV1.L3 " Delay Setting [--]" → ">Delay Setting [32]<" → puis configurer le temps de retard du pulse lors d'un Trigger NIV1.L4 " Trig. Setting [--]" → ">Trig. Setting [32]<" → idem pour la configuration du Trigger