PulseGenerator : Developpement cote CPLD : Programmes de test

Câblage des broches

Le tableau suivant donne la correspondance entre les signaux SPI et les broches du connecteur Pmod:

Module SPI du CPLD implémenté sur le connecteur Pmod J1

| Signaux SPI | CPLD Signal Name | Connecteur Pmod CPLD | Connecteur Pmod PIC32 |

|---|---|---|---|

| SS | SS | J1-IO1 | JD-01 |

| MOSI | MOSI | J1-IO2 | JD-02 |

| MISO | MISO | J1-IO3 | JD-03 |

| SCLK | SCLK | J1-IO4 | JD-04 |

Extrait du fichier SPI_com_Test.ucf sur le SVN

NET "SS" LOC = "P10" ; # connecteur J1 pin 1 (SS)

NET "MOSI" LOC = "P7" ; # connecteur J1 pin 2 (SDO ou MOSI)

NET "MISO" LOC = "P5" ; # connecteur J1 pin 3 (SDI ou MISO)

NET "SCLK" LOC = "P3" ; # connecteur J1 pin 4 (SCLK)

Code exemple - SPI esclave 8 bits, mode 0

Communication SPI entre la carte chipKIT™ Pro MX7 et la carte CoolRunner-II, voir ..\Groupe_FPGA_CPLD\Tutoriel\SPI_Slave_v01

SPI_com_TEST_1

Architecture générale

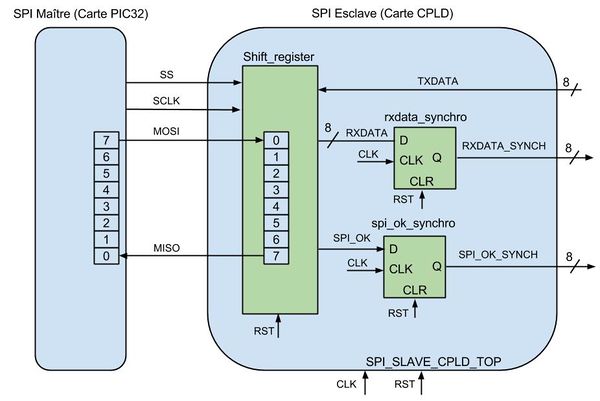

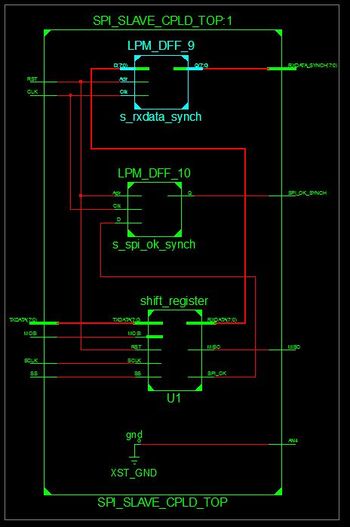

La Figure ci-dessous présente l'architecture globale du module "SPI_SLAVE_CPLD_TOP".

Module "SPI_SLAVE_CPLD_TOP"

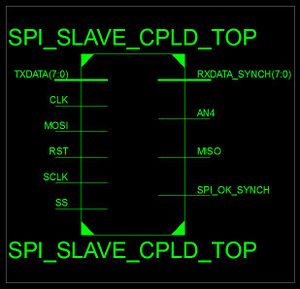

Voici la vue schématique RTL généré automatiquement par l'environnement ISE. Elle comporte autant les signaux utilisés pour l'interface SPI (SS, SCLK, MOSI, MISO) que les signaux internes nécessaires au bon fonctionnement du module "SPI_SLAVE_CPLD_TOP" (RST, CLK,AN4, TXDATA, RXDATA_SYNCH, SPI_OK_SYNCH).

Entrées:

- TXDATA : mot binaire de 8 bits envoyé par l’esclave (le CPLD) au maître (le PIC32).

- CLK : signal logique périodique de fréquence 8 MHz fourni par le quartz présent sur la carte CPLD.

- MOSI : le signal Master Output Slave Input est généré par le maître.

- RST : entrée d’initialisation permettant de forcer le système dans un état de départ dit « état initial ». Il est actif au niveau bas.

- SCLK : signal logique de fréquence 1 MHz fourni par le maître (le PIC).

- SS : Slave Select, actif à l’état bas, généré par le maître pour sélectionner l'esclave avec qu’il veut communiquer.

Sorties:

- RXDATA : mot binaire de 8 bits envoyé par le PIC au CPLD.

- AN4 : permet de sélectionner l'afficheur 7 segment A4 de la carte CPLD.

- MISO : le signal Master Input, Slave Output est généré par l’esclave (le CPLD).

- SPI_OK_SYNCH : passe à ‘1’ lorsqu’on a reçu les 8 coups d’horloge « SCLK ».

Rôle:

Permet de gérer la communication SPI entre le maître (le PIC) et l’esclave (le CPLD).

Architecture du module "SPI_SLAVE_CPLD_TOP"

Module "Shift_register"

Entrées:

- TXDATA : mot binaire de 8 bits envoyé par l’esclave (le CPLD) au maître (le PIC).

- MOSI : le signal Master Output Slave Input est généré par le maître.

- RST : entrée d’initialisation permettant de forcer le système dans un état de départ dit « état initial ». Il est actif au niveau bas.

- SCLK : signal logique de fréquence 1 MHz fourni par le maître (le PIC).

- SS : Slave Select, actif à l’état bas, généré par le maître pour sélectionner l'esclave avec qu’il veut communiquer.

Sorties:

- RXDATA : mot binaire de 8 bits envoyé par le PIC au CPLD.

- MISO : le signal Master Input, Slave Output est généré par l’esclave (le CPLD).

- SPI_OK : passe à ‘1’ lorsqu’on a reçu les 8 coups d’horloge « SCLK ».

Variables:

- spi_count : nombre entier compris entre 0 et 7. Permet de compter le nombre de coups d’horloge « SCLK ».

- txrx_shift : mot binaire de 8 bits représentant le registre à décalage du SPI.

Rôle:

C’est le bloc le plus important du design, il se compose d’un registre à décalage de 8 bits (txrx_shift) dont les extrémités seront le MOSI (bit 0) et le MISO (bit 7) du bloc esclave "SPI_SLAVE_CPLD_TOP". Il permet de gérer la communication SPI entre le maître (PIC32) et l'esclave (CPLD).

Principe:

A chaque coup d'horloge « SCLK » le maître et l'esclave s'échangent un bit. Après huit coups d'horloges le maître a transmis un octet à l'esclave et vice-versa.

Afin d'expliquer le fonctionnement de ce premier code basé sur le principe du registre à décalage, nous allons prendre un exemple simple.

Considérons l'état initial ou TXDATA, qui est la valeur interne au CPLD à transmettre au SPI Maître, vaut 0x01.

Une fois que le SPI Esclave reçoit le front descendant du signal Slave Select (SS), la communication peut démarrer.

Avant le premier front montant de SCLK .... spi_count = 0; TXRX_SHIFT = 0x01; MOSI = ‘1’; MISO = ‘0’

Au premier front montant de SCLK ........... spi_count = 1, TXRX_SHIFT = 0x03; MOSI = ‘1’; MISO = ‘0’

Au second front montant de SCLK ........... spi_count = 2, TXRX_SHIFT = 0x07; MOSI = ‘1’; MISO = ‘0’

Au troisième front montant de SCLK ........ spi_count = 3, TXRX_SHIFT = 0x0F; MOSI = ‘1’; MISO = ‘0’

Au quatrième front montant de SCLK ....... spi_count = 4, TXRX_SHIFT = 0x1F; MOSI = ‘1’; MISO = ‘0’

Au cinquième front montant de SCLK ....... spi_count = 5, TXRX_SHIFT = 0x3F; MOSI = ‘1’; MISO = ‘0’

Au sixième front montant de SCLK .......... spi_count = 6, TXRX_SHIFT = 0x7F; MOSI = ‘1’; MISO = ‘0’

Au septième front montant de SCLK ........ spi_count = 7, TXRX_SHIFT = 0xFF; MOSI = ‘1’; MISO = ‘0’

Au huitième front montant de SCLK ......... spi_count = 8, TXRX_SHIFT = 0xFF; MOSI = ‘1’; MISO = ‘1’

La valeur 0xFF reçu dans TXRX_SHIFT est alors transférée dans le registre interne RXDATA.

Modules "rxdata_synchro" et "spi_ok_synchro"

Le module "rxdata_synchro" permet de rendre synchrone le signal "RXDATA" avec l'horloge "CLK" du module "SPI_SLAVE_CPLD_TOP".

Et le module "spi_ok_synchro" permet de rendre synchrone le signal "SPI_OK" avec l'horloge "CLK" du module "SPI_SLAVE_CPLD_TOP".

Description des entrées/sorties

Extrait du fichier SPI_SLAVE_CPLD_TOP.ucf sur le SVN

NET "AN4" LOC = "P126" ;

NET "CLK" LOC = "P38" ;

NET "MISO" LOC = "P3" ;

NET "MOSI" LOC = "P5" ;

NET "RST" LOC = "P143" ;

NET "RXDATA_SYNCH<0>" LOC = "P56" ;

NET "RXDATA_SYNCH<1>" LOC = "P53" ;

NET "RXDATA_SYNCH<2>" LOC = "P60" ;

NET "RXDATA_SYNCH<3>" LOC = "P58" ;

NET "RXDATA_SYNCH<4>" LOC = "P57" ;

NET "RXDATA_SYNCH<5>" LOC = "P54" ;

NET "RXDATA_SYNCH<6>" LOC = "P61" ;

NET "RXDATA_SYNCH<7>" LOC = "P59" ;

NET "SCLK" LOC = "P10" ;

NET "SPI_OK_SYNCH" LOC = "P69" ;

NET "SS" LOC = "P7" ;

NET "TXDATA<0>" LOC = "P119" ;

NET "TXDATA<1>" LOC = "P117" ;

NET "TXDATA<2>" LOC = "P115" ;

NET "TXDATA<3>" LOC = "P113" ;

NET "TXDATA<4>" LOC = "P118" ;

NET "TXDATA<5>" LOC = "P116" ;

NET "TXDATA<6>" LOC = "P39" ;

NET "TXDATA<7>" LOC = "P124" ;

SPI_com_TEST_2

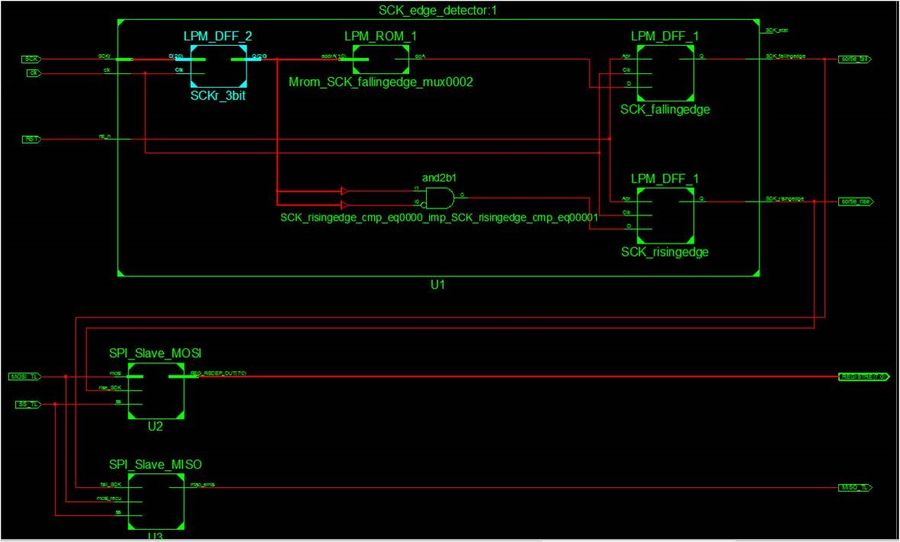

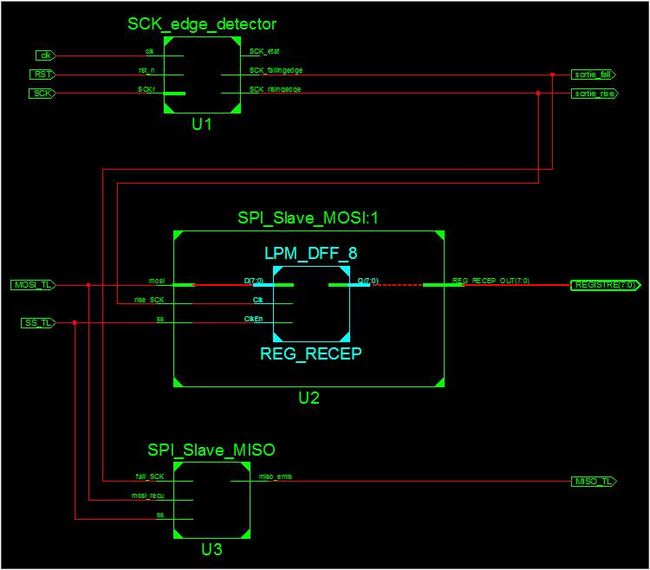

Ce premier projet comporte 4 blocs:

- le top level "Top_level.vhd", équivalent du main en C et 3 sous blocs

- la détection de fronts "SCK_edge_detector.vhdl"

- la gestion du signal "SPI_Slave_MOSI.vhd"

- la gestion du signal "SPI_Slave_MISO.vhd"