PulseGenerator : Cahier des charges

De Wiki_du_Réseau_des_Electroniciens_du_CNRS

<maintab>AccueilProjet Pulse Generator</maintab>

<subtab>PrésentationCahier des chargesGestion du projetCôté PCCôté PICCôté CPLDMembres</subtab>

Page "IHM Hardware", pour suivre et participer à la discussion sur les besoins et propositions autour du prototype v01.

Cahier des charges du générateur d'impulsion

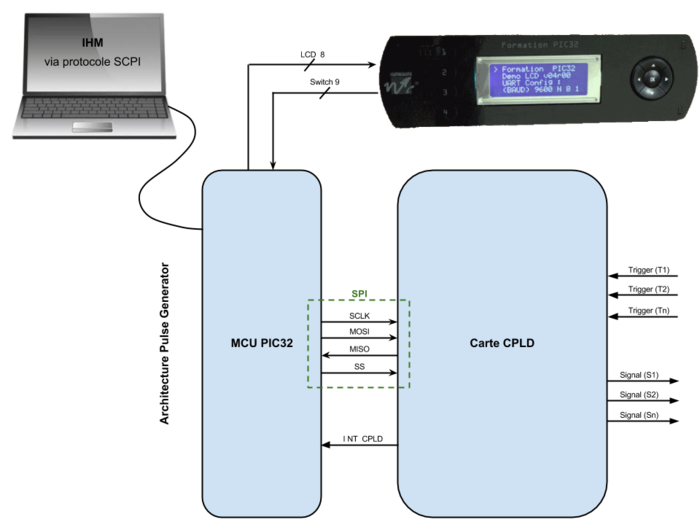

Dessin de l'architecture du Pulse Generator

- liaison SPI 32 bits, mode 0, entre la carte maître PIC32 et la carte esclave CPLD

- sorties numériques (nombre à définir en fonction des bascules disponibles sur la carte CPLD)

- possibilité de Trigger (nombre à définir en fonction des capacités de la carte CPLD)

- largeur des impulsions variables individuellement

- possibilité de retarder le déclenchement de chaque impulsion soit en fonction d’un Trigger, soit en fonction d’une autre voie

- interface de l’instrument (IHM) via un écran LCD 4x20 et un pad 5 touches

- possibilité de contrôle par une interface PC (protocole SCPI)

Exemple de produits commerciaux utilisés en laboratoire

Liens vers les générateurs d’impulsion existant:

Attention, il peut exister une dérive temporelle lors d’utilisation trop longue pour certains appareils, comme sur le master 8. A vérifier donc si cela peut être une contrainte pour vos manip.