FPGA CPLD : Mise en oeuvre du CPLD

Les pré-requis

- Installation de l'environnement de développement

- La documentation du CPLD

- La documentation de la carte de développement

- Le schéma de la carte de développement

- Conception numérique en VHDL

Le tour du propriétaire

La carte CoolRunner-II™ Starter Board

La carte se compose des éléments suivants :

- Un CPLD Xilinx XC2C256 - Package TQ144 - Grade 7C

- Une interface USB Atmel AT90USB162 pour la programmation en JTAG<ref>Il devrait être possible de communiquer avec le CPLD mais cela nécessite d'utiliser les bibliothèques Digilent Adept SDK dont un guide se trouve à cette adresse : https://www.digilentinc.com/Data/Products/ADEPT/DpimRef%20programmers%20manual.pdf</ref>

- Un oscillateur 8 MHz et un emplacement DIP8 libre pour un autre oscillateur

- Une EEPROM Maxim DS28E01A-100 - Communication OneWire

- Un afficheur 7 segments

- 2 boutons poussoirs

- 2 interrupteurs à glissière

- 4 LEDs

- 4 connecteurs PMOD

- 1 port d'extension 32 pins

Il est possible d'alimenter la carte par une alimentation externe en changeant la position du jumper JP2. La programmation peut se faire par l'USB mais aussi en utilisant le connecteur JTAG et le câble approprié (typiquement le Platform Cable USB II ou le JTAG Programming cable)

Lors de la programmation et l'écriture du fichier de contrainte (cf. #Le fichier de contrainte du chapitre #La programmation), vous aurez besoin de connaître le numéro des pins sur lesquelles sont connectés les différents éléments. Vous trouverez la majorité de ces informations dans le manuel de la carte (page 3) et dans le schématique pour les éléments manquants (en particulier le port d'expansion 32 pins).

Le CPLD

Contrairement à un FPGA, la programmation d'un CPLD est non volatile. Vous retrouverez votre programme à l'allumage du composant. Un FPGA nécessite une mémoire externe ou un programmateur pour pouvoir charger son code au démarrage. C'est pour cette raison que la densité des portes logiques programmables est différente entre un CPLD et un FPGA, environ 3/4 des transistors servant à la programmation et la mémorisation dans un CPLD, contre 1/4 dans un FPGA. De plus, le Coolrunner-II™ permet une reprogrammation "On-The-Fly" (cf. la documentation du CPLD) ce qui suppose un espace mémoire (volatile) dédié à cette fonction et qui occupe une partie du composant.

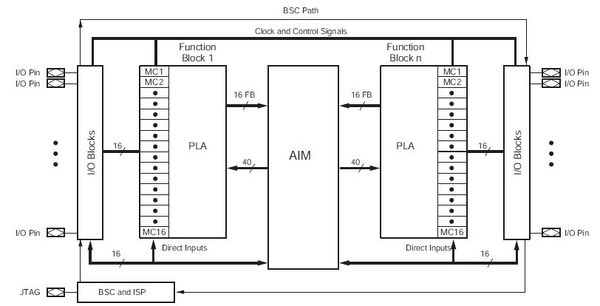

Voici l'architecture interne d'un CPLD Xilinx de type CoolRunner-II™ :

On trouve trois principaux blocs :

- Les blocs d'entrées/sorties (I/O Blocks)

- Les blocs de fonctions (Function Blocks)

- Les matrices d'interconnexion (AIM)

Les blocs d'entrées/sorties

Un bloc d'entrée/sortie peut être configuré de différentes façons. Classiquement, on peut l'utiliser comme une entrée, une sortie ou une entrée/sortie 3 états. On peut y ajouter des options comme une résistance de tirage ou un comparateur à hystérésis. On peut aussi spécifier le type de standard si nécessaire, comme le LVTTL, LVCMOS ou encore HSTL ou SSTL, ces deux derniers nécessitant de câbler la tension Vref.

Les blocs de fonctions

Un bloc de fonctions se compose d'une matrice de logique programmable et d'une macrocell. La matrice sert à créer l'ensemble de la logique combinatoire. La macrocell est l'équivalent d'une bascule D avec en plus un ensemble de signaux de contrôle pour la rendre la plus versatile possible.

Un bloc de fonctions comporte 16 macrocell. Dans notre cas, le composant possède un total de 256 macrocell, donc 16 blocs de fonctions. Chaque bloc de fonctions est connecté à un autre par une matrice d'interconnexion.

La matrice d'interconnexion

La matrice d'interconnexion permet de connecter les blocs de fonctions entre eux. Elles sont l'équivalent d'un énorme multiplexeur crossbar, capable de connecter n'importe quelle sortie d'un bloc de fonctions avec n'importe quelle entrée d'un autre bloc de fonctions adjacent.

Les autres fonctions

Le CPLD se programme avec le protocole JTAG seulement. Le composant USB Atmel fait l'interface USB/JTAG mais n'est pas obligatoire pour programmer le composant car on peut directement se brancher sur le port JTAG avec le câble approprié.

Le CPLD possède deux "bank" d'entrées/sorties. Chaque bank possède sa propre alimentation ce qui permet de faire des CPLD de parfait candidat pour des translateurs de tensions. Dans notre cas, les bank sont connectées à la même alimentation 3,3V (pins VCCIO du schématique).

Il y a trois entrées pour les horloges globales. Les deux premières sont sur des arbres d'horloge classiques. La troisième, GCLK2, peut utiliser un diviseur d'horloge hardware. C'est sur cette dernière qu'est connecté l'oscillateur à 8MHz. On peut aussi multiplier la fréquence par deux en utilisant les fronts montants et descendants des horloges (option DualEDGE).

Il existe aussi une fonction DataGATE qui permet de "geler" certaines parties du design pour réduire la consommation.

Notes

<references/>