Projet DDS

DDS Card AD9858 et ARM TM4C123GH6PM sur liaison USB-SERIE @1MHz Baud Rate

Pour remplacer des cartes d'évaluations Analog device avec un programme souvent non versatile on a développé une source RF entièrement pilotable numériquement grâce à une interface USB-Série et un programme pour microsoft PC C-sharp (dérivé du C++ et très proche du Java,utilisé notamment pour développer des applications web sur la plateforme ASP.NET.). La partie hardware se compose d'un DDS AD9858 @1GHz Clock et d'un uC TEXAS INSTRUMENT TM4C123 @80MHz d'horloge. Un firmware en C à été développé pour le uC qui pilote directement le DDS en mode SPI 3fils @10MHz. L'environnement de programmation est le même que pour le uC développé plus haut, c'est à dire sous IAR Embedded pour ARM. Le programme envoi donc le mot de fréquence (4 Octets) en mode continu ou en single mode, pour réaliser des balayages de fréquences dont la résolution est définie par le nombre de points et le pas entre deux fréquences envoyées par le programme sous C-sharp.

code C firmware pour SPI sur uC TM4C123GH6PM

void ssi0PutData( int instruction,long data,int num_byte)

{

int i=0;

SSI0_DR_R = instruction;

while( num_byte )

{

while(!(SSI0_SR_R & SSI_SR_TNF)) {} // wait until there is space to write in the buffer

SSI0_DR_R = data >>(num_byte-1-i)*8;

num_byte--;

}

while( !( SSI0_SR_R & SSI_SR_TNF ) )

{

;

}

}

void init_SPI0(void)

{

// Enable Peripheral SSI0

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOA); //Enable GPIO port A pins which are used for SSI0.

SysCtlPeripheralEnable(SYSCTL_PERIPH_SSI0);

GPIOPinConfigure(GPIO_PA2_SSI0CLK);

//GPIOPinConfigure(GPIO_PA3_SSI0FSS);

GPIOPinConfigure(GPIO_PA5_SSI0TX);

//GPIOPinTypeSSI(GPIO_PORTA_BASE, GPIO_PIN_5 | GPIO_PIN_3 | GPIO_PIN_2);

GPIOPinTypeSSI(GPIO_PORTA_BASE, GPIO_PIN_5 | GPIO_PIN_2);

SSIConfigSetExpClk(SSI0_BASE, SysCtlClockGet(), SSI_FRF_MOTO_MODE_0, SSI_MODE_MASTER, 10000000, 8);

SSIEnable(SSI0_BASE); // Enable the SSI

}

code C pour initialiser le port série

void init_UART0(void)

{

// Enable Peripheral UART0

SysCtlPeripheralEnable(SYSCTL_PERIPH_UART0);

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOA);

GPIOPinConfigure(GPIO_PA0_U0RX);

GPIOPinConfigure(GPIO_PA1_U0TX);

GPIOPinTypeUART(GPIO_PORTA_BASE, GPIO_PIN_0 | GPIO_PIN_1);

UARTConfigSetExpClk(UART0_BASE, SysCtlClockGet(), 1000000,

(UART_CONFIG_WLEN_8 | UART_CONFIG_STOP_ONE | UART_CONFIG_PAR_NONE));

}

Routine pour les données reçus et transmises

void UART0_send(void)

{

temp[t++] = UART_InChar(); //Read from buffer

if(t >3)

{ write_immediate();

for(t=0;t<4;t++)

{

UART_OutChar(temp[i++]);

}

t = 0; //Reset read length

i = 0;

}

}

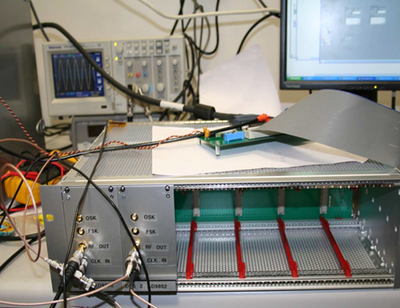

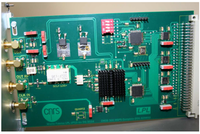

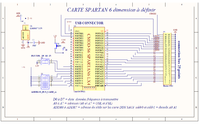

DDS Card AD9852 et AD9858 sur cartes national Instruments DIO 32/64

Description du projet:

Pour une nouvelle expérience du laboratoire, nous avons développé de nouvelles cartes électroniques qui utilisent des composants DDS contrôlés par un ordinateur sur un bus de données numériques. La carte numérique qui contrôle le bus est la carte DIO 32 HS de National Instrument. Ces sources RF programmables à base de technologie DDS seront mises en œuvre sur la nouvelle expérience des atomes froids de l’équipe Gaz Quantique Dipolaire pour conduire les AOM de l'expérience. Pour contrôler les cartes, un programme simple sous LABVIEW a été développé. La principale motivation de ce projet était de construire un système de contrôle pour l'expérience qui permet d'intégrer de nombreuses fonctions avec une interface utilisateur. Les cartes DDS permettront de contrôler avec une bonne synchronisation les différents AOM.

Le bus de données :

Le bus est un bus parallèle de 25 lignes qui est transféré avec un câble plat de 50 lignes, de sorte que les lignes de masses et les lignes de signaux sont alternées. La vitesse du bus dépend des caractéristiques des cartes NI fournies soit de l’ordre de 1/10MHz soit 100ns.Les 16 premières lignes du bus sont les lignes des données et les huit dernières lignes correspondent aux adresses d’appareils (255 en théorie mais 6 bits en pratique et donc 64 appareils adressables).Enfin, la dernière ligne (ligne 25) est l'horloge (STROBE) qui contrôle le débit de données qui est transmis sur le bus. Ce signal met à jour les données et les adresses sur le bus.Ce signal d'horloge doit être présent sur le bus. Programmation des DDS :

Les huit premières lignes de données transmises au DDS sont les DATA : D0-D7 Les huit secondes lignes transmises au DDS sont les ADRESSES : A0-A5 et A6-A7 pour les modes FSK et OSK de l’AD9852 et PS0 PS1 pour l’AD9858. Les huit dernières lignes permettent le décodage d’adresses : decodeA2-decodeA7 Décode au maximum 64 cartes. Les lignes decodeA0 et decodeA1, sont utilisées pour initialisées le DDS de tel sorte que :

A1 A0 = 00 : Master reset DDS

A1 A0 = 01 : Load data DDS

A1 A0 = 10 : I/O update DDS non utilisé si I/O Update interne.

A1 A0 = 11 : non utilisé

Pour initialiser les cartes DDS et transférer les données aux DDS via le bus nous utilisons des composants programmables du type CPLD (circuit logique programmable) associés à des translateurs de niveaux pour passer du niveau TTL (5v) au niveau LVCMOS (3.3v).

Le composant utilisé est un CPLD de la famille XILINX XC2C64A 64 cellules.

Ce composant initialise la carte DDS, assure le décodage d’adresses d’appareils, et surtout la synchronisation des pins du DDS (MASTER RESET, LOAD DATA et I/O UPDATE).

Les cartes DDS disposes de deux CPLD le premier en bas (CPLD1) de la carte pour la synchronisation et l’initialisation du DDS, le deuxième (CPLD2) recopie les données en entrée du bus après autorisation du CPLD1.

La programmation des CPLD se fait grâce à l’environnement ISE design suite 14 ou ultérieur téléchargeable gratuitement sur le site de XILINX (ISE WEB PACK) pour utiliser ISE 14.7 sous windows 10 penser à le patcher.

Ci-joint dans ce document les codes sources pour charger les deux CPLD. Un câble JTAG-USB est indispensable pour la programmation. BUS en fond de panier 25 lignes dont la fréquence de rafraîchissement est d'environ 10MHz et limité par la carte DIO 32 ancienne génération. Chaque carte a une adresse propre (64 max). Le SWITCH DIP 8 sur la carte défini celle-ci. Le code VHDL pour les deux CPLD est simple et modifiable si nécessaire.

Nous avons utilisé une carte FPGA indépendante pour tester les cartes DDS sans le bus numérique : kit utilisé spartan 6 CMODS6. avril 2019

VHDL pour CPLD1 carte DDS AD9852 et bus NI Fichier:VHDL.pdf programme pour tester le bus parallèle et les cartes DDS AD9852 Fichier:Code VHDL pour le spartan 6.pdf

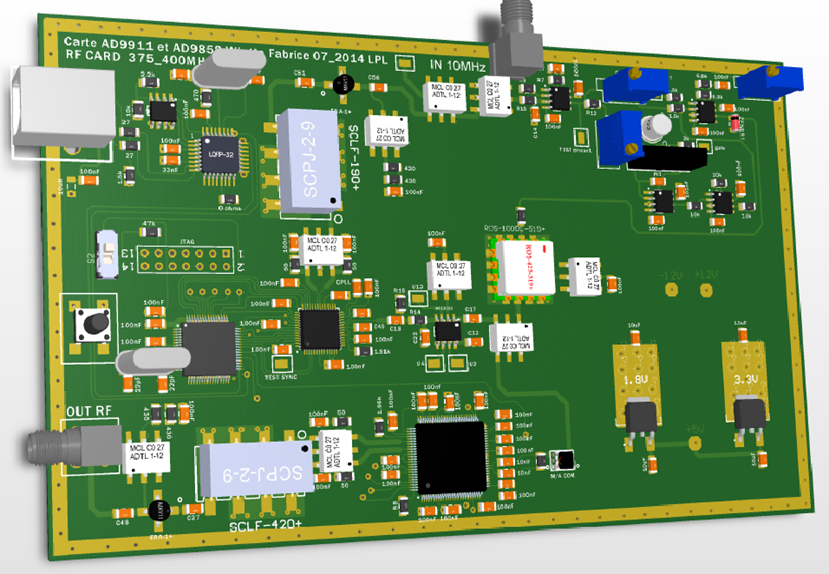

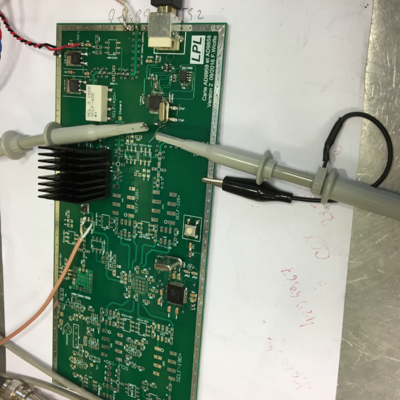

Projet condensat STRONTIUM antenne RF 375-400MHz

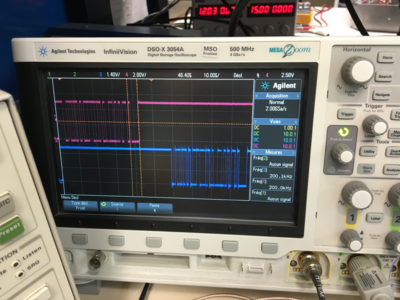

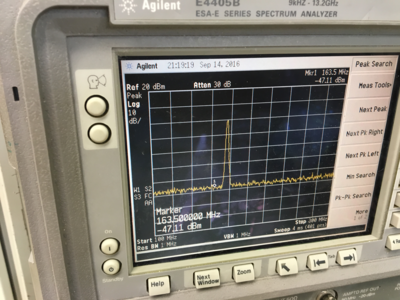

Projet Antenne RF: RF CARD 375 to 400MHz Frequency Sweep control for RF antenna. Le but est de générer des sweeps de fréquence arbitraire pour une antenne RF dans la gamme de fréquence 375 à 400 MHz avec des pas de qqs KHz. J'utilise deux DDS , l'AD9911 pour asservir un VCO ultra low noise à 1GHZ (ROS-1000-519+) minicircuits et le second l'AD9858 pour générer les fréquences arbitraires. Ce dernier est “clocké” grâce au 1GHz provenant du VCO sur la carte. J'utilise également le MSP430F169 pour piloter les deux DDS en mode SPI 2wire single bit (bus SPI commun, un master et deux slaves en utilisant le chip select (CS) de chaques DDS).

Caractéristiques Programmation en mode SPI maître-esclave 2-wire mode single-bit. L’AD9911 et l’AD9858 en mode esclaves via les Chip Select (CS). Horloge commune le ROS-1000C-519@1GHz. Pente de la rampe de fréquence programmée via l’interface CVI. TTL externe commande rampe up et rampe down. Nécessite un signal d’horloge externe 10MHz 5dBm. Une sortie RF (AD9858) programmable 0-400MHz 0dBm.