« Le groupe DDS » : différence entre les versions

m (→Projets LPL) |

|||

| (10 versions intermédiaires par le même utilisateur non affichées) | |||

| Ligne 1 : | Ligne 1 : | ||

< | <div class="subtab">[[Accueil]] - [[Le groupe DDS]]</div><hr/> | ||

| Ligne 37 : | Ligne 36 : | ||

'''Ci-joint le code C du projet:''' gestion affiche LCD + calcul température + fonction standby + contrôle de la consigne de température + lock + timer + déclaration des variables + déclaration prototypes + fichier init système (ADC-DAC TIMER-PORT IN OUT) | '''Ci-joint le code C du projet:''' gestion affiche LCD + calcul température + fonction standby + contrôle de la consigne de température + lock + timer + déclaration des variables + déclaration prototypes + fichier init système (ADC-DAC TIMER-PORT IN OUT) | ||

[[Fichier:vh6010-4_inst_manual.pdf]] | [[Fichier:vh6010-4_inst_manual.pdf]] | ||

[[Fichier:Asservissement en température numérique pour cavité laser ultra-stable.pdf]] | [[Fichier:Asservissement en température numérique pour cavité laser ultra-stable.pdf|thumb|center]] | ||

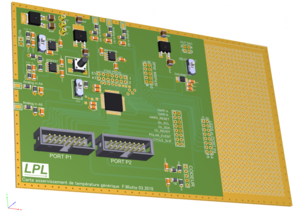

[[Fichier:pcb_asservissement.png]] | [[Fichier:pcb_asservissement.png|thumb|center]] | ||

'''Manipulations d'atomes froids piège magnéto-optique: Coupure rapide de bobine 400A refroidissement eau''' | '''Manipulations d'atomes froids piège magnéto-optique: Coupure rapide de bobine 400A refroidissement eau''' | ||

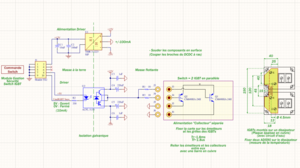

[[Fichier:commande_igbt_400a.png]] | [[Fichier:commande_igbt_400a.png|thumb|center]] | ||

'''Projet complet''': [[Fichier:driverigbt.pdf]] | '''Projet complet''': [[Fichier:driverigbt.pdf]] | ||

| Ligne 210 : | Ligne 209 : | ||

initialisation et chargement des registres CSR et CFTW0: | initialisation et chargement des registres CSR et CFTW0: | ||

<syntaxhighlight lang="c"> | |||

int CSR_ADDRESS = 0x00; AD9959 CSR adresss Byte | int CSR_ADDRESS = 0x00; AD9959 CSR adresss Byte | ||

int CSR_NUM_BYTE = 0x01; CSR nombre d'octet du registre | int CSR_NUM_BYTE = 0x01; CSR nombre d'octet du registre | ||

| Ligne 217 : | Ligne 217 : | ||

int FTW_NUM_BYTE = 0x04; FTW nombre d'octet du registre | int FTW_NUM_BYTE = 0x04; FTW nombre d'octet du registre | ||

long FTW0 = 0x28F5C28F; frequence en hex = fout x2^32/fclock | long FTW0 = 0x28F5C28F; frequence en hex = fout x2^32/fclock | ||

</syntaxhighlight> | |||

dans le main | dans le main | ||

<syntaxhighlight lang="c"> | |||

P4OUT = 0x40; AD9959 master reset bit de validation du MSP430 | P4OUT = 0x40; AD9959 master reset bit de validation du MSP430 | ||

P4OUT = 0x00; AD9959 master set bit de validation du MSP430 | P4OUT = 0x00; AD9959 master set bit de validation du MSP430 | ||

| Ligne 229 : | Ligne 231 : | ||

P5OUT = 0x40; I/O update du DDS bit de validation du MSP430 | P5OUT = 0x40; I/O update du DDS bit de validation du MSP430 | ||

P5OUT = 0x00; I/O update du DDS bit de validation du MSP430 | P5OUT = 0x00; I/O update du DDS bit de validation du MSP430 | ||

</syntaxhighlight> | |||

Commentaires sur le programme: | Commentaires sur le programme: | ||

| Ligne 239 : | Ligne 241 : | ||

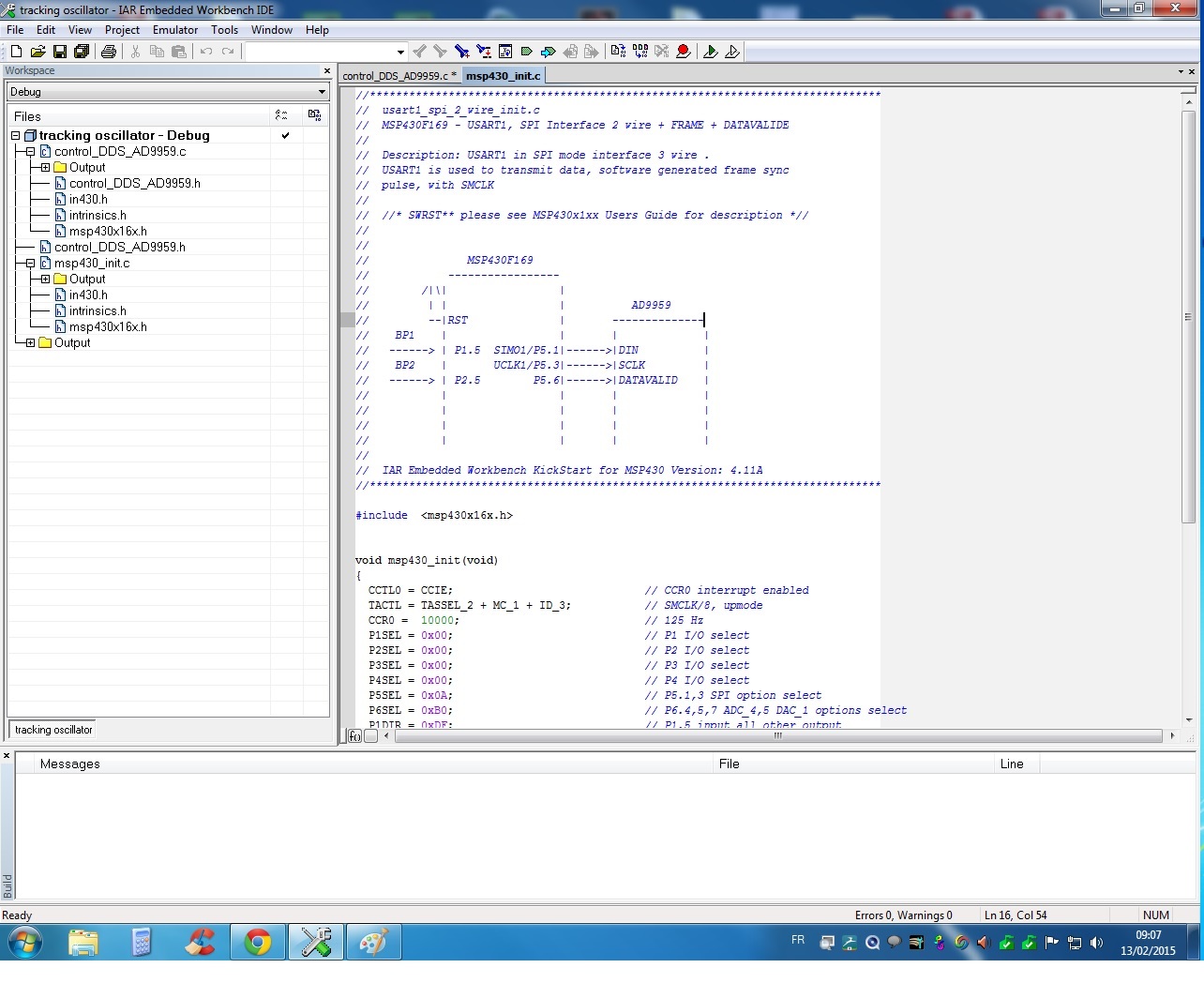

Ci-dessous le sous programme d'initialisation des ports du microcontrôleur et du SPI pour le MSP430F169 : TI fourni de nombreux exemples de codes de bases pour configurer les modes SPI, I2C et utiliser la mémoire Flash: slac015p.zip | Ci-dessous le sous programme d'initialisation des ports du microcontrôleur et du SPI pour le MSP430F169 : TI fourni de nombreux exemples de codes de bases pour configurer les modes SPI, I2C et utiliser la mémoire Flash: slac015p.zip | ||

<syntaxhighlight lang="c"> | |||

#include <msp430x16x.h> | #include <msp430x16x.h> | ||

void DDS_quartz_oscillator_init(void) | void DDS_quartz_oscillator_init(void) | ||

| Ligne 265 : | Ligne 267 : | ||

UCTL1 &= ~SWRST; Initialize USART state machine | UCTL1 &= ~SWRST; Initialize USART state machine | ||

} | } | ||

</syntaxhighlight> | |||

BCSCTL1 |= XTS; et BCSCTL2 |= SELM_3; permet d'être en mode HF XTAL le MSP430 fonctionnera à 8MHZ au lieu de 32KHz par défaut. | BCSCTL1 |= XTS; et BCSCTL2 |= SELM_3; permet d'être en mode HF XTAL le MSP430 fonctionnera à 8MHZ au lieu de 32KHz par défaut. | ||

| Ligne 279 : | Ligne 283 : | ||

= le sous programme pour le chargement des données en mode SPI du MSP430F169 = | = le sous programme pour le chargement des données en mode SPI du MSP430F169 = | ||

<syntaxhighlight lang="c"> | |||

void write_serial_port(int instruction, long data, int num_byte) | void write_serial_port(int instruction, long data, int num_byte) | ||

{ | { | ||

| Ligne 290 : | Ligne 295 : | ||

while (i < num_byte); | while (i < num_byte); | ||

} | } | ||

</syntaxhighlight> | |||

= Un code complet pour charger le DDS avec le MSP430F169 = | = Un code complet pour charger le DDS avec le MSP430F169 = | ||

<syntaxhighlight lang="c"> | |||

#include <msp430x16x.h> | #include <msp430x16x.h> | ||

#include "DDS_quartz_oscillator.h" | #include "DDS_quartz_oscillator.h" | ||

| Ligne 349 : | Ligne 356 : | ||

} | } | ||

} | } | ||

</syntaxhighlight> | |||

ne pas oublier le fichier DDS_quartz_oscillator.h dans le projet pour compiler le programme. | ne pas oublier le fichier DDS_quartz_oscillator.h dans le projet pour compiler le programme. | ||

| Ligne 364 : | Ligne 372 : | ||

= fichier Init MSP430F169 = | = fichier Init MSP430F169 = | ||

[[Fichier:Init MSP430F169.jpg]] | [[Fichier:Init MSP430F169.jpg|center]] | ||

= Projets récents = | = Projets récents = | ||

DDS Card AD9858 on ARM uC TM4C123GH6PM with USB-serial interface@1MHz Baud Rate | DDS Card AD9858 on ARM uC TM4C123GH6PM with USB-serial interface@1MHz Baud Rate | ||

| Ligne 381 : | Ligne 390 : | ||

code C firmware pour SPI sur uC TM4C123GH6PM | code C firmware pour SPI sur uC TM4C123GH6PM | ||

<syntaxhighlight lang="c"> | |||

void ssi0PutData( int instruction,long data,int num_byte) | void ssi0PutData( int instruction,long data,int num_byte) | ||

{ | { | ||

| Ligne 410 : | Ligne 420 : | ||

SSIEnable(SSI0_BASE); // Enable the SSI | SSIEnable(SSI0_BASE); // Enable the SSI | ||

} | } | ||

</syntaxhighlight> | |||

[[Fichier:VISUALISATION SIGNAL RF.png|400px|thumb|left|CARTE DDS sur BUS USB-SERIE 1MHz]] | [[Fichier:VISUALISATION SIGNAL RF.png|400px|thumb|left|CARTE DDS sur BUS USB-SERIE 1MHz]] | ||

code C pour initialiser le port série | code C pour initialiser le port série | ||

<syntaxhighlight lang="c"> | |||

void init_UART0(void) | void init_UART0(void) | ||

{ | { | ||

| Ligne 426 : | Ligne 436 : | ||

(UART_CONFIG_WLEN_8 | UART_CONFIG_STOP_ONE | UART_CONFIG_PAR_NONE)); | (UART_CONFIG_WLEN_8 | UART_CONFIG_STOP_ONE | UART_CONFIG_PAR_NONE)); | ||

} | } | ||

</syntaxhighlight> | |||

=Données reçus et transmises= | =Données reçus et transmises= | ||

<syntaxhighlight lang="c"> | |||

void UART0_send(void) | void UART0_send(void) | ||

{ | { | ||

| Ligne 444 : | Ligne 454 : | ||

} | } | ||

} | } | ||

</syntaxhighlight> | |||

=DDS Card AD9852 and AD9858 sur NI Card DIO 32= | =DDS Card AD9852 and AD9858 sur NI Card DIO 32= | ||

| Ligne 471 : | Ligne 482 : | ||

Les lignes decodeA0 et decodeA1, sont utilisées pour initialisées le DDS de tel sorte que : | Les lignes decodeA0 et decodeA1, sont utilisées pour initialisées le DDS de tel sorte que : | ||

<syntaxhighlight lang="c"> | |||

A1 A0 = 00 : Master reset DDS | A1 A0 = 00 : Master reset DDS | ||

A1 A0 = 01 : Load data DDS | A1 A0 = 01 : Load data DDS | ||

A1 A0 = 10 : I/O update DDS non utilisé si I/O Update interne. | A1 A0 = 10 : I/O update DDS non utilisé si I/O Update interne. | ||

A1 A0 = 11 : non utilisé | A1 A0 = 11 : non utilisé | ||

</syntaxhighlight> | |||

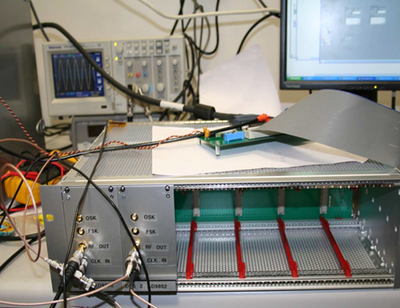

[[Fichier:Châssis 19 pouces.png|400px|thumb|left|CARTES DDS sur BUS NI and DIO32 Card]] | [[Fichier:Châssis 19 pouces.png|400px|thumb|left|CARTES DDS sur BUS NI and DIO32 Card]] | ||

| Ligne 547 : | Ligne 559 : | ||

<syntaxhighlight lang="vhdl"> | |||

'''VHDL pour CPLD1 carte DDS AD9852 et bus NI''' | '''VHDL pour CPLD1 carte DDS AD9852 et bus NI''' | ||

library IEEE; | library IEEE; | ||

| Ligne 658 : | Ligne 677 : | ||

end process; | end process; | ||

end Behavioral; | end Behavioral; | ||

</syntaxhighlight> | |||

=Projet STRONTIUM antenne RF 375-400MHz= | =Projet STRONTIUM antenne RF 375-400MHz= | ||

| Ligne 716 : | Ligne 736 : | ||

Code C pour les routines principales: | Code C pour les routines principales: | ||

<syntaxhighlight lang="c"> | |||

//***************************************************************************** | //***************************************************************************** | ||

// Laboratoire de Physique des Lasers | // Laboratoire de Physique des Lasers | ||

| Ligne 1 066 : | Ligne 1 087 : | ||

} | } | ||

</syntaxhighlight> | |||

=Mesures double DDS 2018= | =Mesures double DDS 2018= | ||

Version du 15 novembre 2018 à 10:13

Introduction

Le but de ce tutoriel est de donner les outils de bases pour démarrer un projet autour d'un DDS, de la programmation à l'implémentation sur circuits imprimés : réalisation de cartes "propriétaires".

Vous pouvez aussi participer à l'enrichissement de cette page avec vos sources ou partager vos projets.

Contacter l'animateur du Groupe DDS par mail Fabrice.wiotte@univ-paris13.fr

http://jmfriedt.free.fr/network_analyzer.pdf : travaux pratiques de Master1 EEA Besançon pour réaliser un petit analyseur de réseau à base d'AD9834 (faible consommation, MCK=75 MHz) commandé par STM32F410.

Projets LPL

Générateur DDS pour asservissement Oscillateur YIG 8-18GHz Fichier:GeneYIG.pdf

General Note on the DDS card and on the BUS driver with labview for AOM control Fichier:NoteBusDDS25042014 2.pdf

Phase shifter with DDS AD9959 Fichier:CARTE AD9959 on USB port pour detection synchrone@30MHz.pdf

Quad SPI control for DDS board with ARM TM4C1294 120MHz (en cours de développement Mars 2018) Fichier:DDS board Quad SPI@60MHz.pdf

Asservissement numérique de température sur cavité laser ultra-stable (projet 2018) Asservissement en température numérique d'une cavité ultra-stable au LPL pour le Strontium condition de stabilité +/- 10mK Résultas obtenus : 1mk sur la journée Compte tenu des constantes de temps d'intégration nous avons opté pour un lock numérique avec un uC 16 bits. ADC et DAC 12 bits MSP430F169 16bits Texas instruments, and IAR Workbench for MSP430 or Code composer studio Cahier des charges: La précision du lock en température devrait être de l'ordre de 10 mK, pour assurer une stabilité en fréquence du laser de l'ordre de quelques kHz. L'élément chauffant a une résistance de 6 Ohm. Un courant de l'ordre de 0.6 A devrait fournir la puissance pour nous amener au point de fonctionnement vers 27°C. Élément de mesure : thermistor MC65F103B Ci-joint le code C du projet: gestion affiche LCD + calcul température + fonction standby + contrôle de la consigne de température + lock + timer + déclaration des variables + déclaration prototypes + fichier init système (ADC-DAC TIMER-PORT IN OUT) Fichier:Vh6010-4 inst manual.pdf Fichier:Asservissement en température numérique pour cavité laser ultra-stable.pdf

Manipulations d'atomes froids piège magnéto-optique: Coupure rapide de bobine 400A refroidissement eau

Projet complet: Fichier:Driverigbt.pdf

Généralités sur les DDS

Les "Direct Digital Synthesizers" (DDS) sont des synthétiseurs qui peuvent générer des formes d'ondes arbitraires à diverses fréquences à partir d'une fréquence de référence fixe.

Une bonne note expliquant le fonctionnement des DDS se trouve ici : Média:Tuto_dds.pdf

Pourquoi les DDS

Depuis quelques années pour les équipes de recherches du Laboratoire de Physique des Lasers (LPL), nous utilisons la technologie DDS pour développer des générateurs radiofréquences de quelques MHz à plusieurs centaines de MHz nécessaires au fonctionnement des expériences, ainsi qu'à l'étude et au développement des Condensats d'atomes froids (BEC). Cette technologie au travers de composants spécifiques, nous permet de réaliser des cartes électroniques adaptées aux expériences du laboratoire. Ces dernières sont entièrement pilotable numériquement, on peut ainsi programmer les paramètres principaux tel que la fréquence, la phase et l’amplitude. Les caractéristiques de ces composants font qu’ils disposent d'une grande pureté spectrale, d’une grande stabilité, d’un faible bruit de phase et d’une grande agilité en fréquence sans saut de phase. Les applications: Générateurs de fonctions, oscillateur local, PLL, driver AOM...

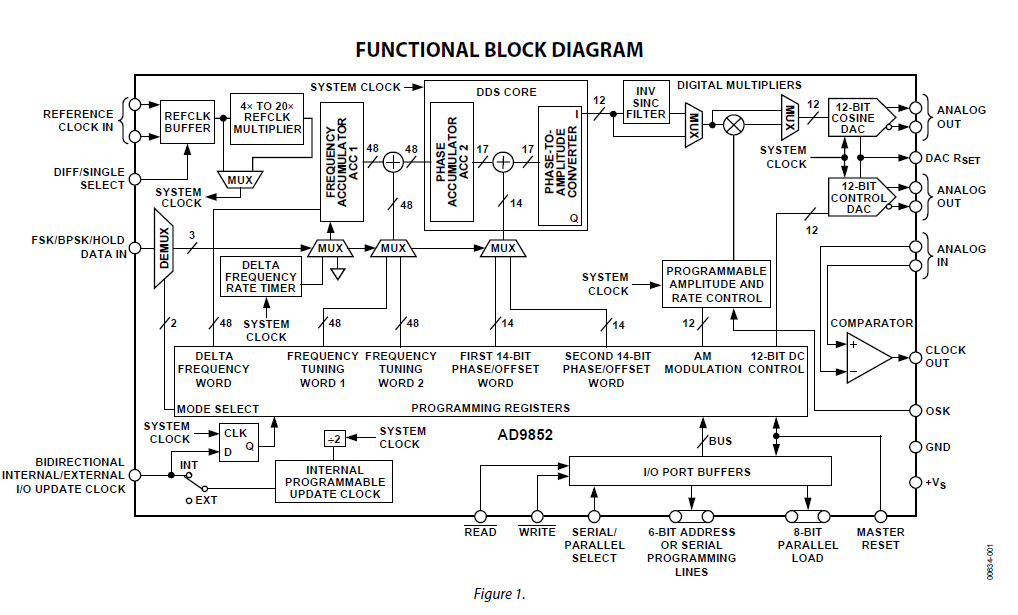

- Ci-dessous schéma fonctionnel de l'AD9852.

- 1.1 Description des principales fonctions d'entrées et de sorties.

REFERENCE CLOCK IN si l'horloge externe = 20MHz PLL activée x 15 = 300MHz (fréquence du system clock) ou si PLL off horloge externe max =300MHz. MASTER RESET bit actif sur front logic 1 initialise le DDS et met la sortie RF à zéro. ANALOG OUT est la sortie RF principale 0dBm en général. I/O UPDATE CLOCK est le bit de chargement des données dans le DDS (par défaut généré en interne et synchronisé sur system clock. FSK/BPSK/HOLD bit actif sur front logic 1 lance les rampes de fréquences en autres. OSK bit actif sur front logic 1 lance les rampes d'amplitudes. 8-BIT PARALLEL LOAD bus 8bits pour chargement des données actif si mode parallèle sélectionné. 6-BIT ADDRESS OR SERIAL PROGRAMMING bus 6bits pour chargement des adresses en mode parallèle sinon utiliser seulement bit A0 pour le mode SPI. SERIAL/PARALLEL SELECT bit de sélection des modes de programmation du DDS: = 1 si chargement parallèle, 0 si chargement série(pin 70 du DDS). DIFF/SINGLE SELECT bit de sélection single ended or differential clock input. pin 64 du DDS. WRITE OR WR/SCLK si mode Parallèle => bit de chargement I/O port buffers, actif sur front descendant ou SCLK en mode SPI.

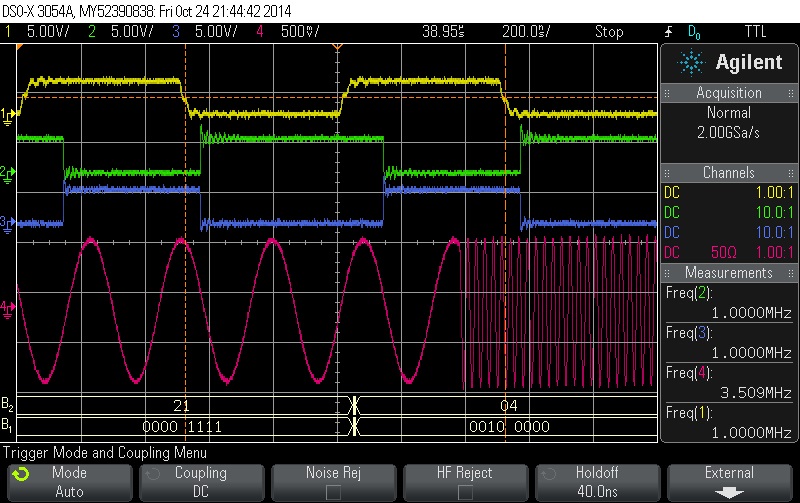

Visualisation d'une sortie d'un DDS (AD9852)

Ci-dessus visualisation du changement de la fréquence de sortie d'un DDS sans saut de phase. Mode de programmation parallèle: en bas de l'écran bus de données(B1) et bus d'adresses(B2). Attention dans cet exemple je ne programme que l'octet de poids fort pour la fréquence et l'amplitude.

En jaune signal d'actualisation des données et adresses, en rouge sortie RF sur 50ohms.

En vert signal WR/SCLK bit de chargement dans I/O port buffers actif sur front descendant et durée minimale programmable = 50ns.

En bleu I/O UPDATE données transmises au DDS actif sur front montant et durée minimale programmable = 50ns.

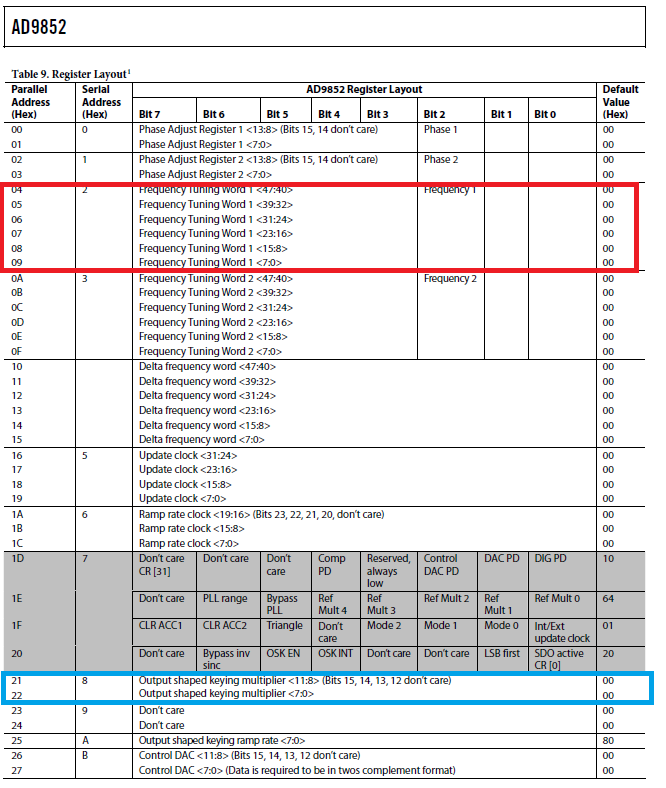

Les courbes en vert et bleu sont volontairement décalées suivant la procédure de chargement des données fournie dans le datasheet du DDS(page 18 du datasheet AD9852).le mot de fréquence pour ce DDS est codé sur 48 bits et donc 6 Octets avec pour parallel address: 0x04;0x05;0x06;0x07;0x08;0x09 (0x04 Octet de poids fort)ou serial address= 0x02 en mode SPI. le mot d'amplitude pour ce DDS est codé sur 12 bits et donc 2 Octets avec pour parallel address:0x21;0x22; (0x21 Octet de poids fort) ou serial address= 0x07 en mode SPI.

Comment programmer un DDS

Une des pages importantes dans un datasheet de DDS est la page register layout table.

celle-ci définie tous les registres à utiliser pour programmer l'ensemble des fonctions de bases.

En rouge le mot de fréquence f1 programmable 48 bits soit sur 6 Octets. En bleu le mot d'amplitude programmable sur 12 bits soit sur 2 Octets. Ce sont les deux paramètres à programmer à minima pour générer un signal RF en sortie.

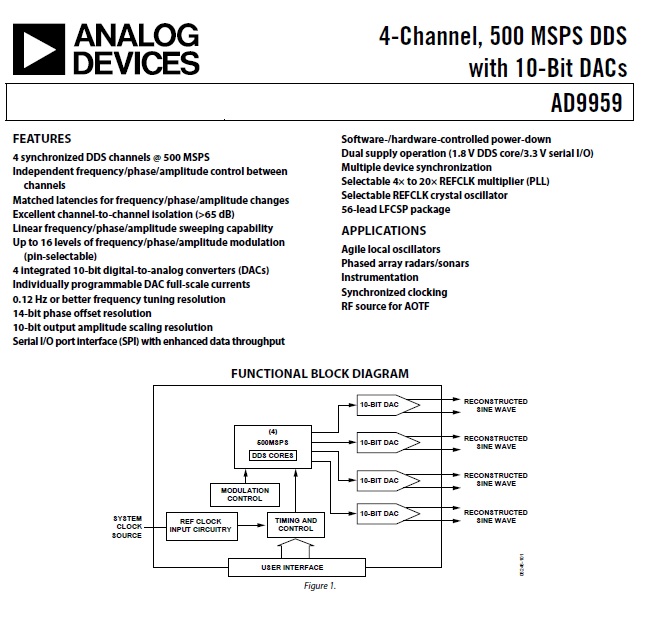

un DDS utilisé au LPL : l'AD9959

Une Application concrète au service électronique du LPL

Un MICROCONTROLEUR 16bits MSP430F169 avec un DDS 4 voies l'AD9959

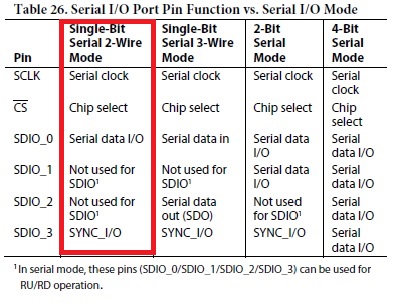

Comment programmer le DDS

La programmation sur ce DDS est uniquement en mode SPI:

Single-bit serial 2-wire mode (default mode)

Single-bit serial 3-wire mode

2-bit serial mode

4-bit serial mode (SYNC_I/O not available)

Côté MSP430F169 : Les sorties SIMO1 P5.1, UCLK1 P5.3 et ACLK P5.6 sont utilisées pour programmer en mode SPI 2 fils (mode par défaut du DDS)

Côté DDS AD9959: SCLK, SDIO_0 et CS/ sont à connecter au microcontrôleur. ci-dessous le mode par défaut.SDIO_1,2 et 3 sont connectés au microcontrôleur pour réaliser si on le souhaite, des profiles de rampes de fréquences ou de phases.

SCLK = serial clock pin 48 du DDS CS/ = Chip select pin 47 du DDS SDIO_0 = Serial data I/O pin 50 du DDS

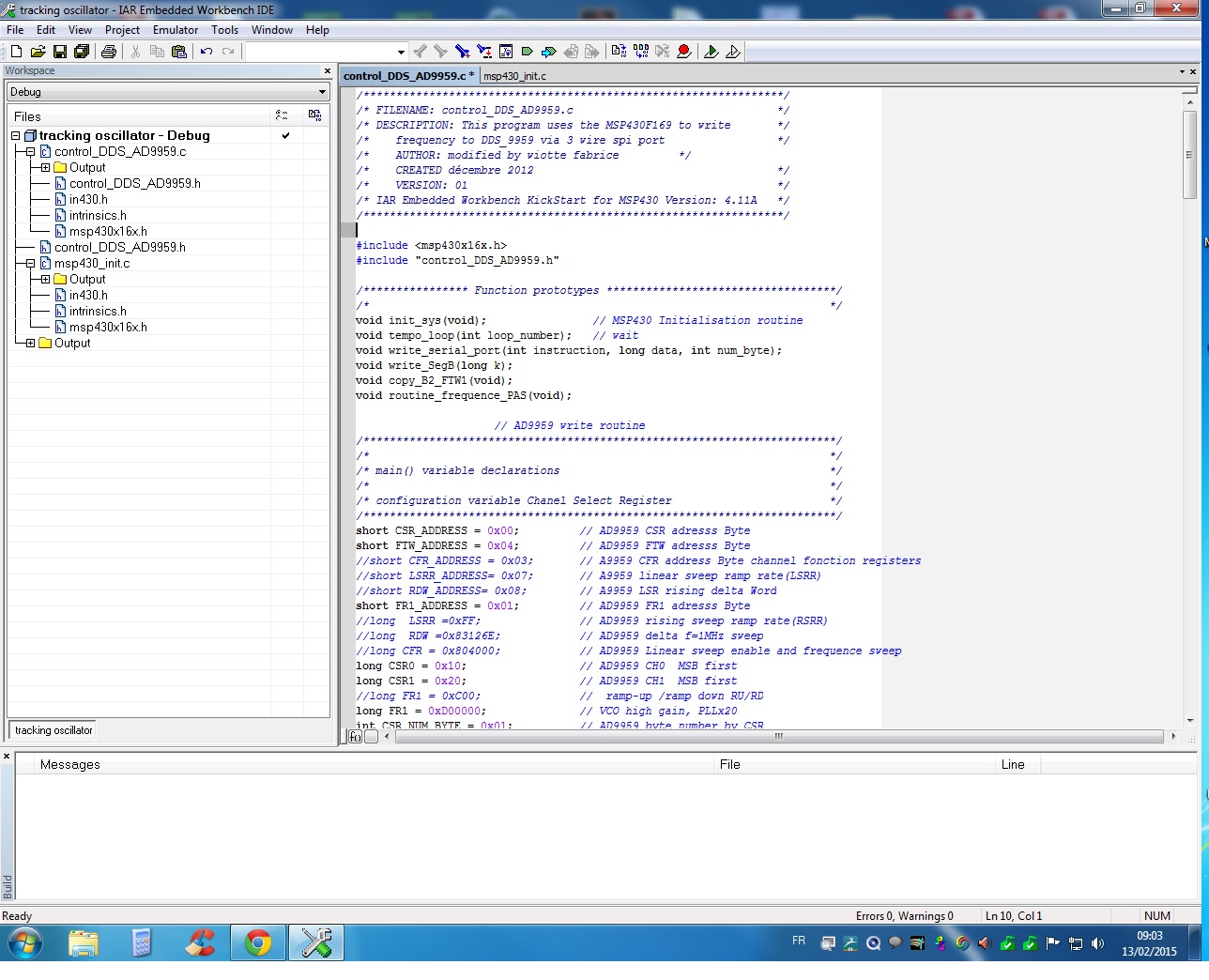

Quel microcontrôleur?

le DDS est programmé par l'intermédiaire d'un microcontrôleur 16 bits de chez TI,le MSP430F169 @8MHz d'horloge. l'environnement de programmation du MSP430 est IAR Embedded Workbench téléchargeable gratuite dans sa version de base. Je conseil d'acheter le kit de débogage MSP430USB MSP-FET430UIF qui permet un débogage pas à pas pratique. Bien entendu bien d'autres microcontrôleurs peuvent êtres utilisés à partir du moment que l'on dispose au moins d'un port SPI. Un développement récent avec l'AD9959 à été réalisé avec un microcontrôleur ATMEL ARDUINO DUE,microcontrôleur 32 bits ARM @84MHz. avec chargement SPI 4 fils. Les dernières cartes développées utilisent un microcontrôleur TEXAS TM4C123GH6PM ARM® Cortex®-M4F Based MCU TM4C123G.

Les différents registres du DDS l'AD9959

table 28 du datasheet de l'AD9959

registre CSR (channel select register) One byte is assigned to this register: le nombre d'octets du registre ici 1 octet. CSR serial address = 0x00; CSR defaut value = 0xF0;

Ce registre active les voies de sorties et les modes SPI: Par défaut toutes les voies sont activées et le mode SPI Single-bit serial 2-wire est sélectionné. Il est évidemment possible de redéfinir ce registre suivant son application.

Le second registre est le registre FR1: table 28 du datasheet registre FR1 (fonction register 1) three bytes is assigned to this register: nombre d'octets du registre FR1 serial address = 0x01; FR1 defaut value = 0x00;

Ce registre permet en autres de définir la PLL interne et le coefficient multiplicateur x4 à x20. Pour exemple la valeur à fournir pour activer la PLL x20 ⇒ FR1 = 0xD00000; Dans ce cas il suffit de fournir un quartz à 25MHz avec la PLL activée x20 on a 500MHz d'horloge PIN 22 et 23 du DDS.

Le troisième registre est le registre CFR table 29 du datasheet registre CFR (Channel Function Register) three bytes is assigned to this register: nombre d'octets du registre CFR serial address = 0x03; CFR defaut value =0x302;

Ce registre défini les différents mode de fonctionnement du DDS.Ce registre est important si vous utiliser certains modes de fonctionnement: balayage de fréquence, de phase, ou d'amplitude. Important par défaut les sortie sont en mode DAC full-scale current.

Le quatrième registre est le registre CFTW0: table 29 du datasheet registre CFTW0 (Channel Frequency Tuning Word 01) four bytes is assigned to this register: nombre d'octets du registre CFTW0 serial address = 0x04; CFTW0 defaut value =0x00;

Ce registre permet de rentrer la fréquence désirée suivant la relation ci-dessous:

FTW0 = frequency output x 2^32 /frequency clock en Hexadecimal

Le cinquième registre est le registre CPOW0 table 29 du datasheet registre CPOW0 (Channel Phase Offset Word 01) two bytes is assigned to this register: nombre d'octets du registre CPOW0 serial address = 0x05; CPOW0 defaut value =0x00;

Ce registre définie la phase du signal de sortie codé sur 14 bits avec la relation ci-dessous:

CPOW0 = Delta phi x 2^14 /360°

Le sixième registre est le registre ACR: table 29 du datasheet registre ACR (Amplitude Control Register) two bytes is assigned to this register: nombre d'octets du registre ACR serial address = 0x06; ACR defaut value =0x00;

Ce registre permet de définir l'amplitude. Par défaut l'amplitude est en mode full scale mais programmable si on modifie le registre CFR.

Les autres registres sont utiles pour programmer le DDS pour des balayages de fréquences, de phases et d'amplitudes en autres.

Registre FR2 (Function Register 2) Registre LSRR (Linear Sweep Ramp Rate1) Registre FDW (LSR Falling delta Word1) Registre RDW (LSR Risingdelta Word1) Registre CW1 (Channel Word 1) ...

Exemple de programme en C écrit dans le microcontrôleur MSP430F169

initialisation et chargement des registres CSR et CFTW0:

int CSR_ADDRESS = 0x00; AD9959 CSR adresss Byte

int CSR_NUM_BYTE = 0x01; CSR nombre d'octet du registre

long CSR0 = 0x10; AD9959 du channel 0 MSB first SPI par défaut

int FTW_ADDRESS = 0x04; AD9959 FTW adresss Byte

int FTW_NUM_BYTE = 0x04; FTW nombre d'octet du registre

long FTW0 = 0x28F5C28F; frequence en hex = fout x2^32/fclock

dans le main

P4OUT = 0x40; AD9959 master reset bit de validation du MSP430

P4OUT = 0x00; AD9959 master set bit de validation du MSP430

write_serial_port(CSR_ADDRESS, CSR0, CSR_NUM_BYTE);

P5OUT = 0x40; I/O update du DDS bit de validation du MSP430

P5OUT = 0x00; I/O update du DDS bit de validation du MSP430

write_serial_port(FTW_ADDRESS, FTW0, FTW_NUM_BYTE);

P5OUT = 0x40; I/O update du DDS bit de validation du MSP430

P5OUT = 0x00; I/O update du DDS bit de validation du MSP430

Commentaires sur le programme:

on fait un RESET du DDS (pin 3), on charge les données de chaque registre au travers du port SPI write_serial_port… Puis on réalise un I/O UPDATE pin 46 du DDS pour la validation et le transfert des données. Ce bout de programme permet de charger le channel 0 avec une fréquence de 80MHz et une amplitude par défaut FULL DAC.

I/O_UPDATE is synchronous to the SYNC_CLK (Pin 54) = Master clock/4. Voir figure 40 du datasheet du DDS.

Ci-dessous le sous programme d'initialisation des ports du microcontrôleur et du SPI pour le MSP430F169 : TI fourni de nombreux exemples de codes de bases pour configurer les modes SPI, I2C et utiliser la mémoire Flash: slac015p.zip

#include <msp430x16x.h>

void DDS_quartz_oscillator_init(void)

{

BCSCTL1 |= XTS; ACLK= LFXT1= HF XTAL

BCSCTL2 |= SELM_3; MCLK = LFXT1 (safe) pin 8,9 du MSP430

P1SEL = 0x00; P1 I/O select

P2SEL = 0x00; P2 I/O select

P3SEL = 0x00; P3 I/O select

P4SEL = 0x00; P4 I/O select

P5SEL = 0x0A; P5.1,3 SPI option select

P6SEL = 0x00; P6 I/O select

P1DIR = 0xFF; P1.output direction

P2DIR = 0xFF; P2 output direction

P3DIR = 0xFF; P3 output direction

P4DIR = 0xFF; P4 output direction

P5DIR = 0xFF; P5 output direction

P6DIR = 0xFF; P6 output direction

ME2 |= USPIE1; Enable USART1 SPI

UCTL1 |= CHAR + SYNC + MM; 8-bit SPI Master **SWRST**

UTCTL1 = CKPH + SSEL1 + STC; SMCLK delayed, 3-pin

UBR01 = 0x2; ACLK/2 for baud rate

UBR11 = 0x0; ACLK/2 for baud rate

UMCTL1 = 0x0; Clear modulation

UCTL1 &= ~SWRST; Initialize USART state machine

}

BCSCTL1 |= XTS; et BCSCTL2 |= SELM_3; permet d'être en mode HF XTAL le MSP430 fonctionnera à 8MHZ au lieu de 32KHz par défaut.

MSP430F169

-----------------

/|\| XIN|-

| | | HF XTAL (455k - 8Mhz)

--|RST XOUT|-

| |

| P5.4|-->MCLK = XTAL

D'après : M. Buccini Texas Instruments Inc. Feb 2005 Built with CCE Version: 3.2.0 and IAR Embedded Workbench Version: 3.21A

le sous programme pour le chargement des données en mode SPI du MSP430F169

void write_serial_port(int instruction, long data, int num_byte)

{

int i=0;

TXBUF1 = instruction;

do

{

TXBUF1 = data >>(num_byte-1-i)*8;

i++;

}

while (i < num_byte);

}

Un code complet pour charger le DDS avec le MSP430F169

#include <msp430x16x.h>

#include "DDS_quartz_oscillator.h"

void init_sys(void); MSP430 Initialisation routine

void tempo_loop(int loop_number); wait loop

void write_serial_port1(int instruction, long data, int num_byte);

/ main() variable declarations /

/ configuration Channel Select Register /

Channel Select Register

int CSR_ADRESS = 0x00; AD9959 CSR adresss Byte

long CSR = 0x10; AD9959 CH0 only MSB first

int CSR_NUM_BYTE = 0x01; AD9959 byte number by CSR

int FTW0_ADRESS = 0x04; AD9959 FTW0 adresss Byte

long FTW0 = 0x38C9138C; AD9959 Frequency Tuning Word0 122MHz

int FTW_NUM_BYTE = 0x04; AD9959 byte number by FTW

void main(void)

{

/ initialisation du msp430 /

init_sys(); Initialise the MSP430

tempo_loop(10000); wait loop

P5OUT = 0x00;

P4OUT = 0x40; Reset AD9959

tempo_loop(10000); wait loop

P4OUT = 0x00; Set AD9959

write_serial_port1(CSR_ADRESS, CSR, CSR_NUM_BYTE);

tempo_loop(100); wait loop

P5OUT = 0x40; AD9959 I/O update

P5OUT = 0x00;

write_serial_port1(FTW0_ADRESS, FTW0, FTW_NUM_BYTE);

tempo_loop(10); wait loop

P5OUT = 0x40; AD9959 I/O update

P5OUT = 0x00;

}

void init_sys(void)

{

WDTCTL = WDTPW + WDTHOLD; // stop Watch Dog Timer

DDS_quartz_oscillator_init(); // init usart1, spi mode, 2wire

}

void write_serial_port1(int instruction, long data, int num_byte)

{

int i=0;

TXBUF1 = instruction;

do

{

TXBUF1 = data >>(num_byte-1-i)*8;

i++;

}while (i < num_byte);

}

void tempo_loop(int loop_number)

{

int i;

int j;

for(i = 0; i < loop_number; ++i) wait loop

{

j=j+i;

}

}

ne pas oublier le fichier DDS_quartz_oscillator.h dans le projet pour compiler le programme.

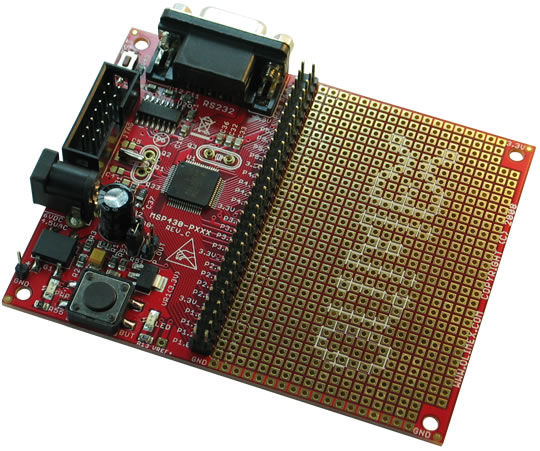

Un kit de prototypage

MPS430F169 HEADER BOARD olimex Price 22.95 EUR

IAR for MSP430

fichier Init MSP430F169

Projets récents

DDS Card AD9858 on ARM uC TM4C123GH6PM with USB-serial interface@1MHz Baud Rate

DDS Card AD9852 and AD9858 on BUS NATIONAL INSTRUMENTS and labview program

DDS Card AD9858 on ARM uC TM4C123GH6PM with USB-serial interface@1MHz Baud Rate

Pour remplacer des cartes d'évaluations Analog device avec un programme souvent non versatile on a développé une source RF entièrement pilotable numériquement grâce à une interface USB-Série et un programme pour microsoft PC C-sharp (dérivé du C++ et très proche du Java,utilisé notamment pour développer des applications web sur la plateforme ASP.NET.). La partie hardware se compose d'un DDS AD9858 @1GHz Clock et d'un uC TEXAS INSTRUMENT TM4C123 @80MHz d'horloge. Un firmware en C à été développé pour le uC qui pilote directement le DDS en mode SPI 3fils @10MHz. L'environnement de programmation est le même que pour le uC développé plus haut, c'est à dire sous IAR Embedded pour ARM. Le programme envoi donc le mot de fréquence (4 Octets) en mode continu ou en single mode, pour réaliser des balayages de fréquences dont la résolution est définie par le nombre de points et le pas entre deux fréquences envoyées par le programme sous C-sharp.

code C firmware pour SPI sur uC TM4C123GH6PM

void ssi0PutData( int instruction,long data,int num_byte)

{

int i=0;

SSI0_DR_R = instruction;

while( num_byte )

{

while(!(SSI0_SR_R & SSI_SR_TNF)) {} // wait until there is space to write in the buffer

SSI0_DR_R = data >>(num_byte-1-i)*8;

num_byte--;

}

while( !( SSI0_SR_R & SSI_SR_TNF ) )

{

;

}

}

void init_SPI0(void)

{

// Enable Peripheral SSI0

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOA); //Enable GPIO port A pins which are used for SSI0.

SysCtlPeripheralEnable(SYSCTL_PERIPH_SSI0);

GPIOPinConfigure(GPIO_PA2_SSI0CLK);

//GPIOPinConfigure(GPIO_PA3_SSI0FSS);

GPIOPinConfigure(GPIO_PA5_SSI0TX);

//GPIOPinTypeSSI(GPIO_PORTA_BASE, GPIO_PIN_5 | GPIO_PIN_3 | GPIO_PIN_2);

GPIOPinTypeSSI(GPIO_PORTA_BASE, GPIO_PIN_5 | GPIO_PIN_2);

SSIConfigSetExpClk(SSI0_BASE, SysCtlClockGet(), SSI_FRF_MOTO_MODE_0, SSI_MODE_MASTER, 10000000, 8);

SSIEnable(SSI0_BASE); // Enable the SSI

}

code C pour initialiser le port série

void init_UART0(void)

{

// Enable Peripheral UART0

SysCtlPeripheralEnable(SYSCTL_PERIPH_UART0);

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOA);

GPIOPinConfigure(GPIO_PA0_U0RX);

GPIOPinConfigure(GPIO_PA1_U0TX);

GPIOPinTypeUART(GPIO_PORTA_BASE, GPIO_PIN_0 | GPIO_PIN_1);

UARTConfigSetExpClk(UART0_BASE, SysCtlClockGet(), 1000000,

(UART_CONFIG_WLEN_8 | UART_CONFIG_STOP_ONE | UART_CONFIG_PAR_NONE));

}

Données reçus et transmises

void UART0_send(void)

{

temp[t++] = UART_InChar(); //Read from buffer

if(t >3)

{ write_immediate();

for(t=0;t<4;t++)

{

UART_OutChar(temp[i++]);

}

t = 0; //Reset read length

i = 0;

}

}

DDS Card AD9852 and AD9858 sur NI Card DIO 32

Description du projet

Pour une nouvelle expérience du laboratoire, nous avons développé de nouvelles cartes électroniques qui utilisent des composants DDS contrôlés par un ordinateur sur un bus de données numériques. La carte numérique qui contrôle le bus est la carte DIO 32 HS de National Instrument. Ces sources RF programmables à base de technologie DDS seront mises en œuvre sur la nouvelle expérience des atomes froids de l’équipe Gaz Quantique Dipolaire pour conduire les AOM de l'expérience. Pour contrôler les cartes, un programme simple sous LABVIEW a été développé. La principale motivation de ce projet était de construire un système de contrôle pour l'expérience qui permet d'intégrer de nombreuses fonctions avec une interface utilisateur. Les cartes DDS permettront de contrôler avec une bonne synchronisation les différents AOM.

Le bus de données :

Le bus est un bus parallèle de 25 lignes qui est transféré avec un câble plat de 50 lignes, de sorte que les lignes de masses et les lignes de signaux sont alternées. La vitesse du bus dépend des caractéristiques des cartes NI fournies soit de l’ordre de 1/10MHz soit 100ns. Les 16 premières lignes du bus sont les lignes des données et les huit dernières lignes correspondent aux adresses d’appareils (255 en théorie mais 6 bits en pratique et donc 64 appareils adressables). Enfin, la dernière ligne (ligne 25) est l'horloge (STROBE) qui contrôle le débit de données qui est transmis sur le bus. Ce signal met à jour les données et les adresses sur le bus. Ce signal d'horloge doit être présent sur le bus.

Programmation des DDS :

Les huit premières lignes de données transmises au DDS sont les DATA : D0-D7 Les huit secondes lignes transmises au DDS sont les ADRESSES : A0-A5 et A6-A7 pour les modes FSK et OSK de l’AD9852 et PS0 PS1 pour l’AD9858. Les huit dernières lignes permettent le décodage d’adresses : decodeA2-decodeA7 Décode au maximum 64 cartes. Les lignes decodeA0 et decodeA1, sont utilisées pour initialisées le DDS de tel sorte que :

A1 A0 = 00 : Master reset DDS

A1 A0 = 01 : Load data DDS

A1 A0 = 10 : I/O update DDS non utilisé si I/O Update interne.

A1 A0 = 11 : non utilisé

Pour initialiser les cartes DDS et transférer les données aux DDS via le bus nous utilisons des composants programmables du type CPLD (circuit logique programmable) associés à des translateurs de niveaux pour passer du niveau TTL (5v) au niveau LVCMOS (3.3v).

Le composant utilisé est un CPLD de la famille XILINX XC2C64A 64 cellules.

Ce composant initialise la carte DDS, assure le décodage d’adresses d’appareils, et surtout la synchronisation des pins du DDS (MASTER RESET, LOAD DATA et I/O UPDATE).

Les cartes DDS disposes de deux CPLD le premier en bas (CPLD1) de la carte pour la synchronisation et l’initialisation du DDS, le deuxième (CPLD2) recopie les données en entrée du bus après autorisation du CPLD1.

La programmation des CPLD se fait grâce à l’environnement ISE design suite 14 ou ultérieur téléchargeable gratuitement sur le site de XILINX (ISE WEB PACK) ;

Ci-joint dans ce document les codes sources pour charger les deux CPLD. Un câble JTAG-USB est indispensable pour la programmation.

BUS en fond de panier 25 lignes dont la fréquence de rafraîchissement est d'environ 10MHz et limité par la carte DIO 32 ancienne génération. Chaque carte a une adresse propre (64 max). Le SWITCH DIP 8 sur la carte défini celle-ci.Le code VHDL pour les deux CPLD est simple et modifiable si nécessaire.

'''VHDL pour CPLD1 carte DDS AD9852 et bus NI'''

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.all;

use IEEE.STD_LOGIC_UNSIGNED.all;

entity '''addressbus_and_decode''' is

GENERIC (n: INTEGER := 20);

Port (

ADDR_BUS_in : in STD_LOGIC_VECTOR (5 downto 0);

A0_A1_address: in STD_LOGIC_VECTOR (1 downto 0);

STROBE : in STD_LOGIC;

MASTER_CLOCK : in STD_LOGIC;

STROBE_OUT : out STD_LOGIC;

--IO_UPDATE : out STD_LOGIC; -- par défaut mode dds

RD : out STD_LOGIC;

LOAD_DATA : out STD_LOGIC;

MASTER_RESET : out STD_LOGIC;

SP_MODE : out STD_LOGIC;

CONTROL_DIP8 : in STD_LOGIC_VECTOR (5 downto 0)

);

end addressbus_and_decode;

'''architecture Behavioral of addressbus_and_decode is'''

SIGNAL internal: STD_LOGIC_VECTOR (n-1 DOWNTO 0);

SIGNAL STROBE_OUT_bis : STD_LOGIC;

SIGNAL SEL0 : STD_LOGIC;

SIGNAL SEL1 : STD_LOGIC;

SIGNAL SEL2 : STD_LOGIC;

SIGNAL SEL3 : STD_LOGIC;

SIGNAL reset : STD_LOGIC;

SIGNAL load : STD_LOGIC;

begin

SP_MODE <='1';

RD <='1';

--registre a décalage Tempo STROBE générérateur de temporisation pour décalage

'''PROCESS(MASTER_CLOCK,STROBE)'''

BEGIN

IF (STROBE ='0') THEN

internal <= (OTHERS => '0');

ELSIF (MASTER_CLOCK'EVENT AND MASTER_CLOCK='1') THEN

internal <= STROBE & internal(internal'LEFT DOWNTO 1);

END IF;

END PROCESS;

-- 2 bits address A0 et A1 decoder 2 to 4 and control ADDR = CONTROL_dip8

'''process(A0_A1_address,ADDR_BUS_in,CONTROL_DIP8)'''

begin

if internal(15) ='1' and ADDR_BUS_in = CONTROL_DIP8 then

case A0_A1_address is

when "00"=> SEL0 <='1'; SEL1<='0'; SEL2<='0'; SEL3<='0';

when "01"=> SEL0 <='0'; SEL1<='1'; SEL2<='0'; SEL3<='0';

when "10"=> SEL0 <='0'; SEL1<='0'; SEL2<='1'; SEL3<='0';

when "11"=> SEL0 <='0'; SEL1<='0'; SEL2<='0'; SEL3<='1';

when others => SEL0 <='Z'; SEL1<='Z'; SEL2 <='Z'; SEL3 <='Z';

end case;

else

SEL0 <='Z'; SEL1<='Z'; SEL2 <='Z'; SEL3 <='Z';

end if;

end process;

STROBE_OUT <= STROBE_OUT_bis;

--STROBE out pour autorisation sur CPLD2 latchs décalage de 50ns /strobe

'''process(internal(15),ADDR_BUS_in,CONTROL_DIP8)'''

begin

if internal(15) ='1' and ADDR_BUS_in = CONTROL_DIP8 and SEL0 ='0' then

STROBE_OUT_bis <='1';

else

STROBE_OUT_bis <='0';

end if;

end process;

-- control bit MASTER_RESET décalage de 50ns /strobe

'''process(internal(15),SEL0,ADDR_BUS_in,CONTROL_DIP8)'''

begin

if internal(15) = '1' and SEL0 ='1' and ADDR_BUS_in = CONTROL_DIP8 then

MASTER_RESET <= '1';

else

MASTER_RESET <= '0';

end if;

end process;

-- control bit Load data into IO buffer(WR) décalage de 100ns /strobe

'''process(internal(10),SEL1,ADDR_BUS_in,CONTROL_DIP8)'''

begin

if internal(10)= '1' and SEL1 ='1' and ADDR_BUS_in = CONTROL_DIP8 then

LOAD_DATA <= '0';

else

LOAD_DATA <= '1';

end if;

end process;

end Behavioral;

'''VHDL pour CPLD2 AD9852 et AD9858'''

--Programme CPLD2 pour AD9852 et AD9858—

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity test_cpld_haut is

Port (

DATA_in : in STD_LOGIC_VECTOR (7 downto 0);

ADDRESS_in : in STD_LOGIC_VECTOR (7 downto 0);

DATA_out : out STD_LOGIC_VECTOR (7 downto 0);

ADDRESS_out : out STD_LOGIC_VECTOR (7 downto 0);

STROBE_in : in STD_LOGIC

);

end test_cpld_haut;

architecture '''Behavioral of test_cpld_haut''' is

begin

-- octal 2 d-type latches 3 états, 8bits

'''process(STROBE_in,DATA_in,ADDRESS_in)'''

begin

if STROBE_in ='1' then

DATA_out <= DATA_in;

ADDRESS_out <= ADDRESS_in;

end if;

end process;

end Behavioral;

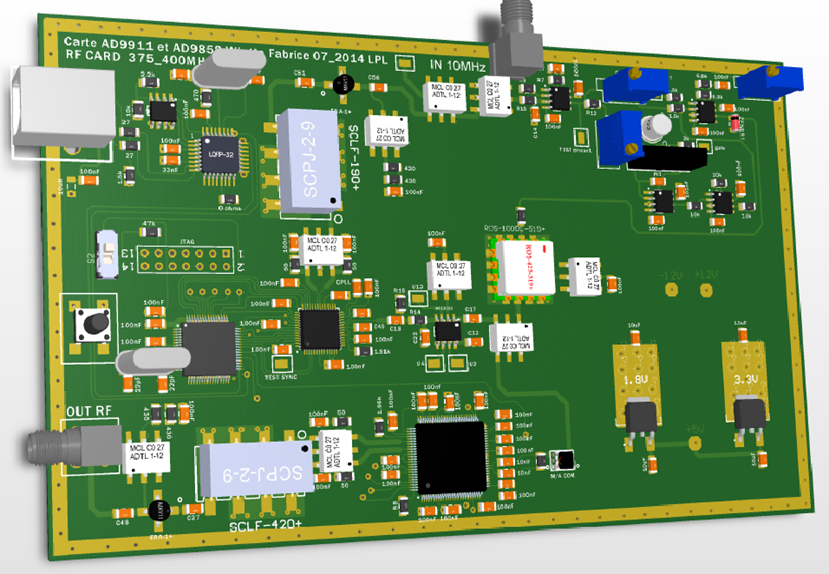

Projet STRONTIUM antenne RF 375-400MHz

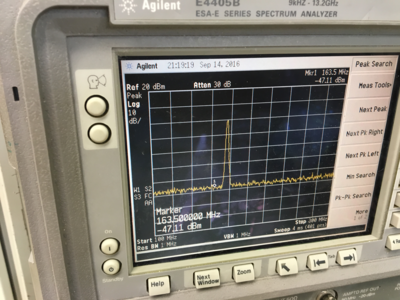

Projet Antenne RF: RF CARD 375 to 400MHz Frequency Sweep control for RF antenna. Le but est de générer des sweeps de fréquence arbitraire pour une antenne RF dans la gamme de fréquence 375 à 400 MHz avec des pas de qqs KHz. J'utilise deux DDS , l'AD9911 pour asservir un VCO ultra low noise à 1GHZ (ROS-1000-519+) minicircuits et le second l'AD9858 pour générer les fréquences arbitraires. Ce dernier est “clocké” grâce au 1GHz provenant du VCO sur la carte. J'utilise également le MSP430F169 pour piloter les deux DDS en mode SPI 2wire single bit (bus SPI commun, un master et deux slaves en utilisant le chip select (CS) de chaques DDS).

Caractéristiques

Programmation en mode SPI maître-esclave 2-wire mode single-bit. L’AD9911 et l’AD9858 en mode esclaves via les Chip Select (CS). Horloge commune le ROS-1000C-519@1GHz. Pente de la rampe de fréquence programmée via l’interface CVI. TTL externe commande rampe up et rampe down. Nécessite un signal d’horloge externe 10MHz 5dBm. Une sortie RF (AD9858) programmable 0-400MHz 0dBm.

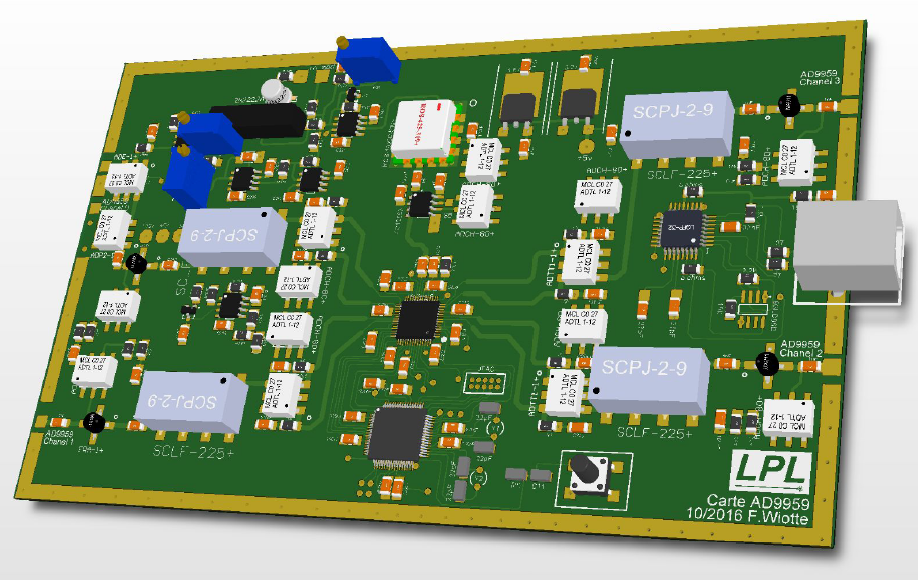

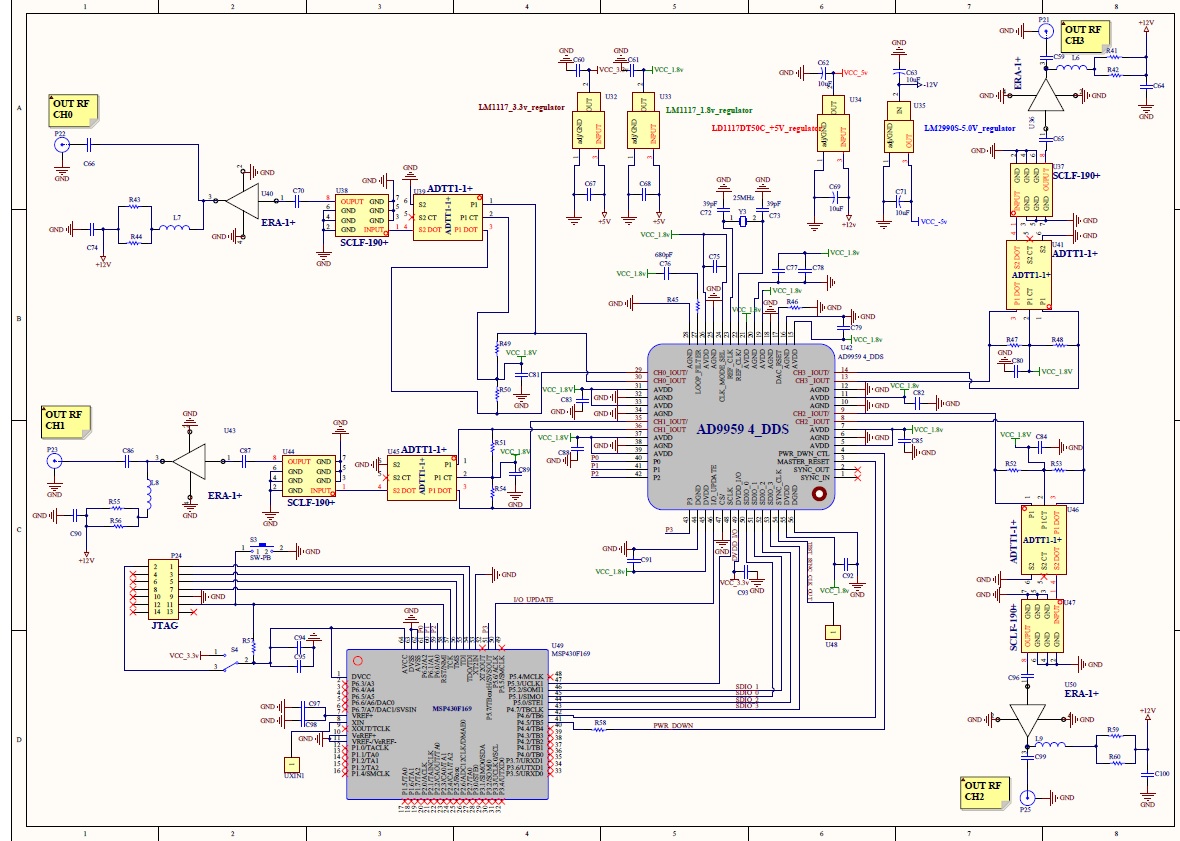

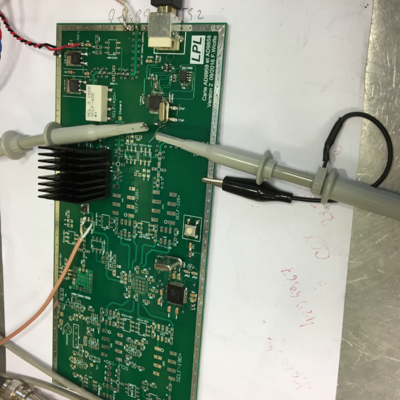

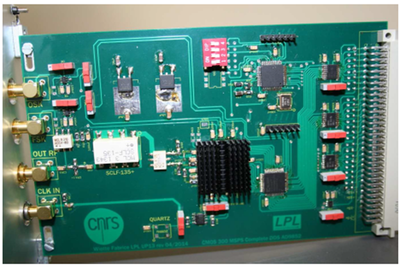

Projet diffusion Raman expérience CHROME

Conception et réalisation d'un ensemble de deux pilotes acous-optiques d'une puissance unitaire de 2W. L'objectif est de régler le décalage en fréquence de deux faisceaux "Raman" corrélés en phase. Réalisation de deux sources RF@80MHz en corrélation de phase avec une fréquence centrale de 80MHz. Pilotage sur liaison USB-Série@10MHz (en cours de tests). Les signaux RF sont synchronisés sur une même horloge@500MHz à l'aide d'un DDS AD9959 qui dispose de plusieurs sorties RF basse puissance (5dBm).Les circuits sont implémentés sur des cartes au format Europe et insérées dans un châssis 19 pouces entièrement réalisé à l'atelier d'électronique.

Projet Générateur RF autonome deux voies à partir de puce DDS AD9959

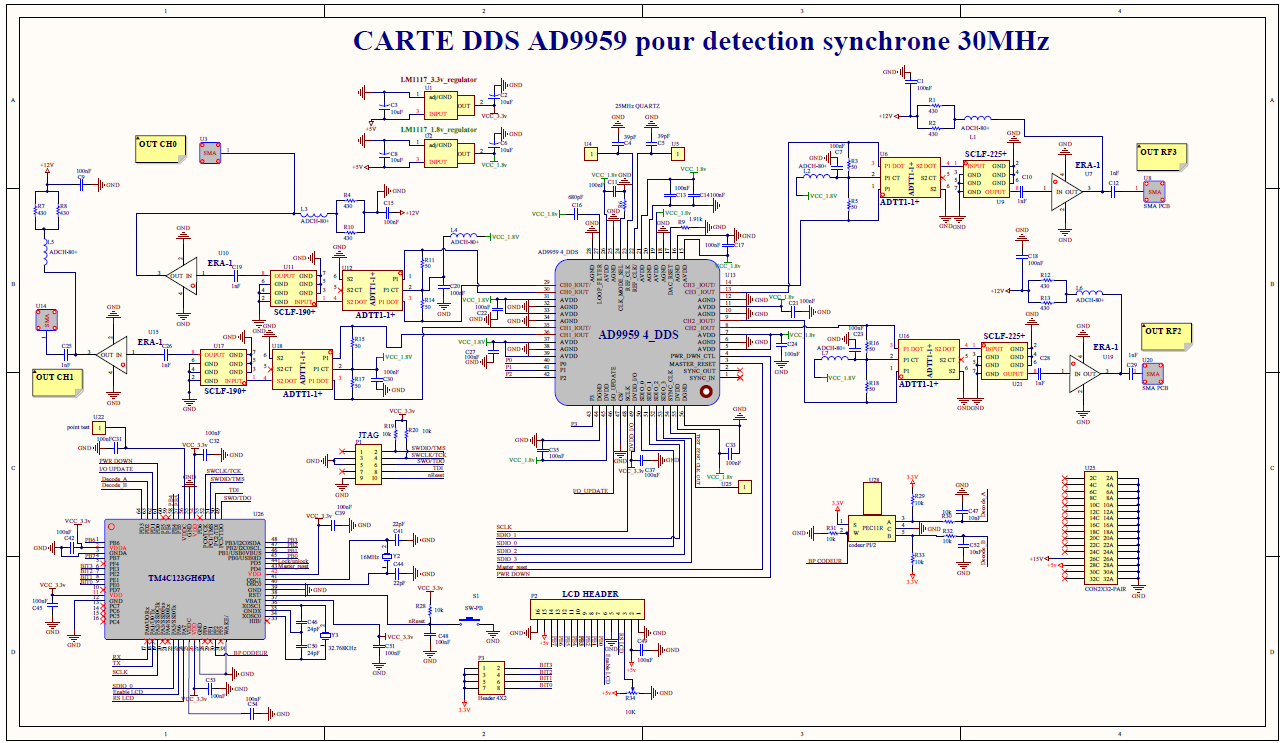

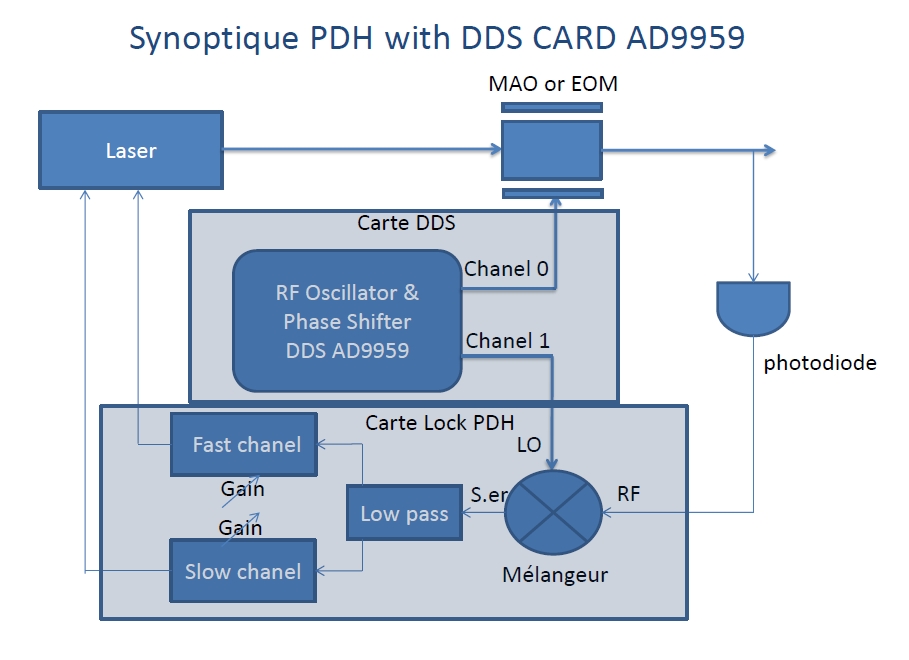

1.DDS pour détection synchrone et asservissement PDH

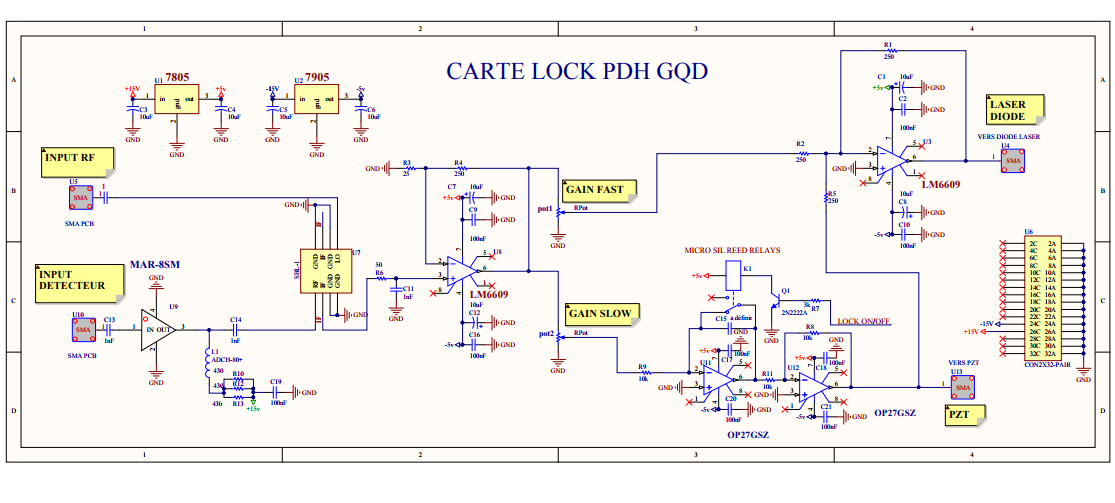

Système de lock laser sur cavité ultra stable voir synoptique ci-dessous:

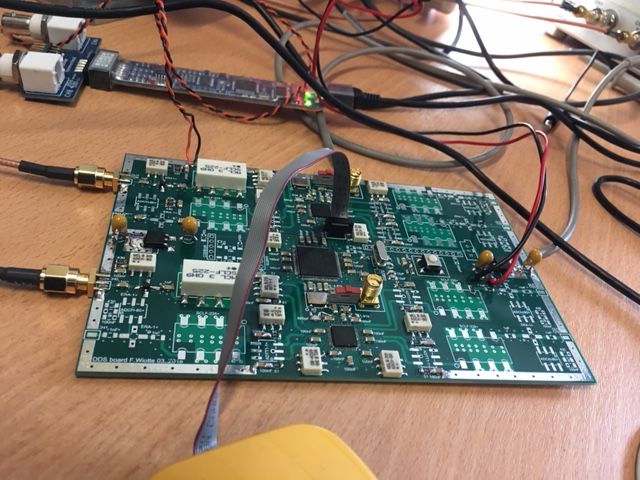

DDS card for PDH AD9959 on uC TM4C123 and LCD 2x16 and codeur Gray

Programme ARM for PDH

Fichier:Programme uC TM4C123GH6PM for PDH module.pdf

Carte partie Lock

Carte partie DDS

Double DDS AD9959 sur port SPI quad @60MHz Projet 2018

Développement 2018 : Piège RF Pour des considérations de vitesse d’exécution et de chargement des données nous avons fait évoluer les cartes DDS pour l'expérience BEC du LPL. La programmation des DDS est réalisé en Quad SPI à une vitesse de 60MHz. les données sont transmises au uC (ARM 120MHz) grâce à l'interface USB-UART non représentée sur le PCB ci-dessous à une vitesse de 10Mbps.

8 sorties RF programmables:

Code C pour les routines principales:

//*****************************************************************************

// Laboratoire de Physique des Lasers

// Wiotte Fabrice

// Ingénieur d'étude CNRS

// Service Electronique D002 Rdc

// CNRS – URM7538 – Université Paris 13

// 99 Avenue J.-B. Clément

// 93430 Villetaneuse

// http://www-lpl.univ-paris13.fr/

//

// This is part of revision 2.1.0.12573 of the EK-TM4C1294XL Firmware Package.

//

void init_SPI1_mode_quad_bit(void)

{

// Enable Peripheral SSI1

//if Quad SPI

//***********************//

//GPIO_PE4_SSI1XDAT0 <= BIT 4 BIT 0 only need 2 CLK cycle to send 8bits.

//GPIO_PE5_SSI1XDAT1 <= BIT 5 BIT 1 only need 2 CLK cycle to send 8bits.

//GPIO_PD4_SSI1XDAT2 <= BIT 6 BIT 2 only need 2 CLK cycle to send 8bits.

//GPIO_PD5_SSI1XDAT3 <= BIT 7 BIT 3 only need 2 CLK cycle to send 8bits.

//*************************************//

//Polarity Phase Mode

// 0 0 SSI_FRF_MOTO_MODE_0

// 0 1 SSI_FRF_MOTO_MODE_1

// 1 0 SSI_FRF_MOTO_MODE_2

// 1 1 SSI_FRF_MOTO_MODE_3

//*************************************//

//************************//

// SSI1 is used with the following GPIO Pin Mapping

// SSI1CLK : PB5

// SSI1FSS : PB4

// SSI1XDAT0 : PE4

// SSI1XDAT1 : PE5

// SSI1XDAT2 : PD4

// SSI1XDAT3 : PD5

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOB);

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOD);

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOE);

SysCtlPeripheralEnable(SYSCTL_PERIPH_SSI1);

// Configure the pin muxing for SSI1 functions on port B4, B5, E4, E5,D4, D5

GPIOPinConfigure(GPIO_PB5_SSI1CLK);

GPIOPinConfigure(GPIO_PB4_SSI1FSS);

GPIOPinConfigure(GPIO_PE4_SSI1XDAT0);

GPIOPinConfigure(GPIO_PE5_SSI1XDAT1);

GPIOPinConfigure(GPIO_PD4_SSI1XDAT2);

GPIOPinConfigure(GPIO_PD5_SSI1XDAT3);

/* Configure pad settings */

GPIOPadConfigSet(GPIO_PORTB_BASE, GPIO_PIN_5|GPIO_PIN_4, GPIO_STRENGTH_12MA, GPIO_PIN_TYPE_STD);

GPIOPadConfigSet(GPIO_PORTE_BASE, GPIO_PIN_5|GPIO_PIN_4, GPIO_STRENGTH_12MA, GPIO_PIN_TYPE_STD);

GPIOPadConfigSet(GPIO_PORTD_BASE, GPIO_PIN_5|GPIO_PIN_4, GPIO_STRENGTH_12MA, GPIO_PIN_TYPE_STD);

// Configure the GPIO settings for the SSI pins. This function also gives

// control of these pins to the SSI hardware.

GPIOPinTypeSSI(GPIO_PORTB_BASE,GPIO_PIN_5|GPIO_PIN_4);

GPIOPinTypeSSI(GPIO_PORTE_BASE,GPIO_PIN_5|GPIO_PIN_4);

GPIOPinTypeSSI(GPIO_PORTD_BASE,GPIO_PIN_5|GPIO_PIN_4);

SSIConfigSetExpClk(SSI1_BASE, 120000000, SSI_FRF_MOTO_MODE_0, SSI_MODE_MASTER, 60000000, 8);

//

// Enable the SSI1 module.

//

SSI1_CR1_R = 0x00000080;

SSIEnable(SSI1_BASE);

}

void init_SPI0_mode_quad_bit(void)

{

// Enable Peripheral SSI0

//if Quad SPI

//***********************//

//***********************//

//GPIO_PA4_SSI0XDAT0 <= BIT 4 BIT 0 only need 2 CLK cycle to send 8bits.

//GPIO_PA5_SSI0XDAT1 <= BIT 5 BIT 1 only need 2 CLK cycle to send 8bits.

//GPIO_PA6_SSI0XDAT2 <= BIT 6 BIT 2 only need 2 CLK cycle to send 8bits.

//GPIO_PA7_SSI0XDAT3 <= BIT 7 BIT 3 only need 2 CLK cycle to send 8bits.

//************************//

//*************************************//

//Polarity Phase Mode

// 0 0 SSI_FRF_MOTO_MODE_0

// 0 1 SSI_FRF_MOTO_MODE_1

// 1 0 SSI_FRF_MOTO_MODE_2

// 1 1 SSI_FRF_MOTO_MODE_3

//*************************************//

//************************//

// SSI1 is used with the following GPIO Pin Mapping

// SSI0CLK : PA2

// SSI0FSS : PA3

// SSI0XDAT0 : PA4

// SSI0XDAT1 : PA5

// SSI0XDAT2 : PA6

// SSI0XDAT3 : PA7

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOA);

SysCtlPeripheralEnable(SYSCTL_PERIPH_SSI0);

// Configure the pin muxing for SSI0 functions on port A2, A3, A4, A5, A6, A7

GPIOPinConfigure(GPIO_PA2_SSI0CLK);

GPIOPinConfigure(GPIO_PA3_SSI0FSS);

GPIOPinConfigure(GPIO_PA4_SSI0XDAT0);

GPIOPinConfigure(GPIO_PA5_SSI0XDAT1);

GPIOPinConfigure(GPIO_PA6_SSI0XDAT2);

GPIOPinConfigure(GPIO_PA7_SSI0XDAT3);

/* Configure pad settings */

GPIOPadConfigSet(GPIO_PORTA_BASE, GPIO_PIN_2|GPIO_PIN_3, GPIO_STRENGTH_12MA, GPIO_PIN_TYPE_STD);

GPIOPadConfigSet(GPIO_PORTA_BASE, GPIO_PIN_4|GPIO_PIN_5, GPIO_STRENGTH_12MA, GPIO_PIN_TYPE_STD);

GPIOPadConfigSet(GPIO_PORTA_BASE, GPIO_PIN_6|GPIO_PIN_7, GPIO_STRENGTH_12MA, GPIO_PIN_TYPE_STD);

// Configure the GPIO settings for the SSI pins. This function also gives

// control of these pins to the SSI hardware.

GPIOPinTypeSSI(GPIO_PORTA_BASE,GPIO_PIN_2|GPIO_PIN_3);

GPIOPinTypeSSI(GPIO_PORTA_BASE,GPIO_PIN_4|GPIO_PIN_5);

GPIOPinTypeSSI(GPIO_PORTA_BASE,GPIO_PIN_6|GPIO_PIN_7);

SSIConfigSetExpClk(SSI0_BASE, 120000000, SSI_FRF_MOTO_MODE_0, SSI_MODE_MASTER, 60000000, 8);

SSIAdvModeSet(SSI0_BASE, SSI_ADV_MODE_WRITE);

SSIAdvModeSet(SSI0_BASE,SSI_ADV_MODE_BI_WRITE);

//

// Enable the SSI0 module.

//

SSI0_CR1_R = 0x00000080;

SSIEnable(SSI0_BASE);

}

void init_SPI0_mode_single_bit(void)

{

// Enable Peripheral SSI0

//if Single bit serial mode SPI

//***********************//

// SSI0 is used with the following GPIO Pin Mapping

// SSI1CLK : PA2

// SSI1FSS : PA3

// SSI1XDAT0 : PA4

//************************//

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOA);

SysCtlPeripheralEnable(SYSCTL_PERIPH_SSI0);

GPIOPinConfigure(GPIO_PA2_SSI0CLK);

GPIOPinConfigure(GPIO_PA3_SSI0FSS);

GPIOPinConfigure(GPIO_PA4_SSI0XDAT0);

// Configure the GPIO settings for the SSI pins. This function also gives

// control of these pins to the SSI hardware.

GPIOPinTypeSSI(GPIO_PORTA_BASE,GPIO_PIN_2|GPIO_PIN_3|GPIO_PIN_4);

SSIConfigSetExpClk(SSI0_BASE, 120000000, SSI_FRF_MOTO_MODE_0, SSI_MODE_MASTER, 60000000, 8);

//

// Enable the SSI0 module.

//

SSI0_CR1_R = 0x00000000;

SSIEnable(SSI0_BASE); // Enable the SSI

}

void init_SPI1_mode_single_bit(void)

{

// Enable Peripheral SSI1

//if Single bit serial mode SPI

//***********************//

// SSI1 is used with the following GPIO Pin Mapping

// SSI1CLK : PB5

// SSI1FSS : PB4

// SSI1XDAT0 : PE4

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOB);

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOE);

SysCtlPeripheralEnable(SYSCTL_PERIPH_SSI1);

// Configure the pin muxing for SSI1 functions on port B4, B5, E4,

GPIOPinConfigure(GPIO_PB5_SSI1CLK);

GPIOPinConfigure(GPIO_PB4_SSI1FSS);

GPIOPinConfigure(GPIO_PE4_SSI1XDAT0);

// Configure the GPIO settings for the SSI pins. This function also gives

// control of these pins to the SSI hardware.

GPIOPinTypeSSI(GPIO_PORTB_BASE,GPIO_PIN_5|GPIO_PIN_4);

GPIOPinTypeSSI(GPIO_PORTE_BASE,GPIO_PIN_4);

SSIConfigSetExpClk(SSI1_BASE, 120000000, SSI_FRF_MOTO_MODE_0, SSI_MODE_MASTER, 60000000, 8);

//

// Enable the SSI1 module.

//

SSI1_CR1_R = 0x00000000;

SSIEnable(SSI1_BASE);

}

// init data transfert SPI data to send SSI0

void ssi0PutData( int instruction,long data,int num_byte)

{

int i=0;

SSI0_DR_R = instruction;

while( num_byte )

{

SSI0_DR_R = data >>(num_byte-1-i)*8;

num_byte--;

}

while( !( SSI0_SR_R & SSI_SR_TNF ) )

{

;

}

}

// init data transfert SPI data to send SSI1

void ssi1PutData( int instruction,long data,int num_byte)

{

int i=0;

SSI1_DR_R = instruction;

while( num_byte )

{

SSI1_DR_R = data >>(num_byte-1-i)*8;

num_byte--;

}

while( !( SSI1_SR_R & SSI_SR_TNF ) )

{

;

}

}

void PortH_Init(void) //// Initialize GPIO Port H

{

// activate clock for Port H

SYSCTL_RCGCGPIO_R |= SYSCTL_RCGCGPIO_R7;

// allow time for clock to stabilize

while((SYSCTL_PRGPIO_R&SYSCTL_PRGPIO_R7) == 0){};

GPIO_PORTH_DIR_R = 0x0F; // make PH3-0 out

GPIO_PORTH_AFSEL_R &= ~0x0F; // disable alt funct on PH3-0

//GPIO_PORTH_PUR_R = 0x03; // enable pull-up on

GPIO_PORTH_DEN_R = 0x0F; // enable digital I/O on PH3-0

GPIO_PORTH_PCTL_R &= ~0x0000FFFF; // 4) configure PH3-0 as GPIO

//GPIO_PORTH_AMSEL_R = 0; // disable analog functionality on PH3-0

}

void PortD_Init(void) //// Initialize GPIO Port D

{

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOD);

// activate clock for Port H

SYSCTL_RCGCGPIO_R = SYSCTL_RCGCGPIO_R3; // activate clock for Port D

// allow time for clock to stabilize

while((SYSCTL_PRGPIO_R&SYSCTL_PRGPIO_R3) == 0){};

HWREG(GPIO_PORTD_BASE + GPIO_O_LOCK) = GPIO_LOCK_KEY;

HWREG(GPIO_PORTD_BASE + GPIO_O_CR) = 0x80;

GPIO_PORTD_DIR_R |= 0xFF; // make PD7-0 out

//GPIO_PORTD_AFSEL_R &= ~0x0F; // disable alt funct on PD7-0

//GPIO_PORTD_PUR_R = 0x03; // enable pull-up on

GPIO_PORTD_DEN_R |= 0xFF; // enable digital I/O on PD7-0

GPIO_PORTD_PCTL_R &= ~0xFFFFFFFF; // 4) configure PD7-0 as GPIO

//GPIO_PORTH_AMSEL_R = 0; // disable analog functionality on PD7-0

}

void PortN_Init(void)

{

// activate clock for Port N

SYSCTL_RCGCGPIO_R |= SYSCTL_RCGCGPIO_R12;

// allow time for clock to stabilize

while((SYSCTL_PRGPIO_R&SYSCTL_PRGPIO_R12) == 0){};

GPIO_PORTN_DIR_R |= 0x3F; // make PN5-0 out

GPIO_PORTN_AFSEL_R &= ~0x3F; // disable alt funct on PN5-0

GPIO_PORTN_DEN_R |= 0x3F; // enable digital I/O on PN5-0

// configure PN3-0 as GPIO

GPIO_PORTN_PCTL_R &= ~0xFFFFFFFF; // 4) configure PN7-0 as GPIO

GPIO_PORTN_AMSEL_R &= ~0x3F; // disable analog functionality on PN5-0

}

void PortA_Init(void)

{

// activate clock for Port A

SYSCTL_RCGCGPIO_R |= SYSCTL_RCGCGPIO_R0;

// allow time for clock to stabilize

while((SYSCTL_PRGPIO_R&SYSCTL_PRGPIO_R0) == 0){};

GPIO_PORTA_DIR_R |= 0xC0; // make PA6,7 out

//GPIO_PORTA_AFSEL_R &= ~0xFF; // disable alt funct on PA7-0

GPIO_PORTA_DEN_R |= 0xFF; // enable digital I/O on PA7-0

// configure PA7-0 as GPIO

//GPIO_PORTA_PCTL_R &= ~0xFFFFFFFF; // 4) configure PA7-0 as GPIO

GPIO_PORTA_AMSEL_R &= ~0xFF; // disable analog functionality on PA7-0

}

void PeripheralEnableInit(void)

{

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOA);

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOB);

//SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOC);

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOD);

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOE);

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOH);

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPION);

//SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOF);

}

int main(void)

{

// clock to 120MHz

ui32SysClkFreq = SysCtlClockFreqSet((SYSCTL_XTAL_25MHZ | SYSCTL_OSC_MAIN | SYSCTL_USE_PLL | SYSCTL_CFG_VCO_480), 120000000);

volatile uint32_t ui32Loop;

PeripheralEnableInit();

PortA_Init();

PortD_Init();

PortH_Init();

PortN_Init();

//Enable Peripheral SSI0 single bit SPI

init_SPI0_mode_single_bit();

// make master reset DDS2

PN1 = 0x02; // reset DDS2

SysCtlDelay(200);

PN1 = 0x00;

// data send to SPI0 PORT @60Mbs to two DDS card

ssi0PutData(FR1_ADRESS,FR1,FR1_NUM_BYTE);

ssi0PutData(CSR_ADRESS,0xF0,CSR_NUM_BYTE); //select CH0 and CH1 and CH2 and CH3

ssi0PutData(FTW_ADRESS,0x10624DD,FTW_NUM_BYTE);

ssi0PutData(CSR_ADRESS,0xF6,CSR_NUM_BYTE); //AD9959 CH0 CH1 MSB first 4-bit serial mode

SysCtlDelay(100);

PN0 = 0x01; // AD9959 I/O update

SysCtlDelay(20);

PN0 = 0x00;

//Enable Peripheral SSI0 quad SPI

init_SPI0_mode_quad_bit();

ssi0PutData(FTW_ADRESS,0x51EB851,FTW_NUM_BYTE);

SysCtlDelay(100);

PN0 = 0x01; // AD9959 I/O update

SysCtlDelay(20);

PN0 = 0x00;

//Enable Peripheral SSI1 single bit SPI

init_SPI1_mode_single_bit();

// make master reset DDS1

PN4 = 0x10; // reset DDS1

SysCtlDelay(200);

PN4 = 0x00;

// data send to SPI1 PORT @60Mbs to two DDS card

ssi1PutData(FR1_ADRESS,FR1,FR1_NUM_BYTE);

ssi1PutData(CSR_ADRESS,0xF0,CSR_NUM_BYTE); //select CH0 and CH1 and CH2 and CH3

ssi1PutData(FTW_ADRESS,0x10624DD,FTW_NUM_BYTE);

ssi1PutData(CSR_ADRESS,0xF6,CSR_NUM_BYTE); //AD9959 CH0 CH1 MSB first 4-bit serial mode

SysCtlDelay(100);

PN3 = 0x08; // AD9959 I/O update

SysCtlDelay(20);

PN3 = 0x00;

//Enable Peripheral SSI1 quad SPI

init_SPI1_mode_quad_bit();

ssi1PutData(FTW_ADRESS,0x51EB851,FTW_NUM_BYTE);

SysCtlDelay(100);

PN3 = 0x08; // AD9959 I/O update

SysCtlDelay(20);

PN3 = 0x00;

}

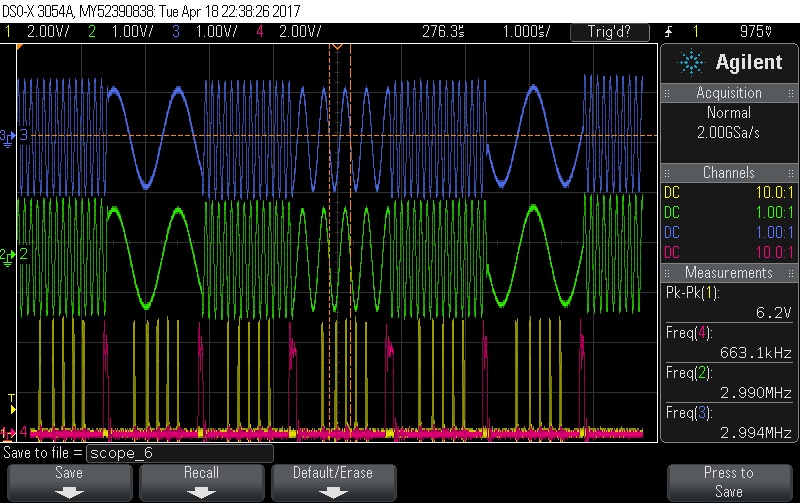

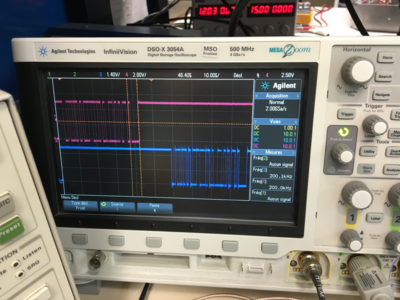

Mesures double DDS 2018

Ci-joint une copie d'écran du taux de transfert en mode 4 fils SPI qui montre la vitesse max des datas sur le port SPI. CLK SPI 60MHz. Test avec des liaisons filaires courtes sur une carte DDS AD9959 voie 0 et 1 activées. En rouge : I/O Update En jaune : CLK data SPI 2 coups d'horloge / Octet transmis. En bleu et vert : chanel 0 et chanel 1.